# CPSS Transactions on **Power Electronics and** Applications

VOLUME 3 NUMBER 3 SEPTEMBER 2018

## SPECIAL ISSUE ON VEHICLE ELECTRIFICATION

### EDITORIAL

### SPECIAL ISSUE PAPERS

| Parameter Identification of Capacitive Power Transfer System Based on Spectrum Analysis         |     |

|-------------------------------------------------------------------------------------------------|-----|

| C. Chen, C. Li, C. Liao, and L. Wang                                                            | 181 |

| Adaptive DC-Link Voltage Control of LLC Resonant ConverterLC. Shih, YH. Liu, and YF. Luo        | 187 |

| Active Power Filter for Single-Phase Quasi-Z-Source Integrated On-Board Charger                 |     |

| T. Na, Q. Zhang, J. Tang, and J. Wang                                                           | 197 |

| Adaptive Charging Strategy With Temperature Rise Mitigation and Cycle Life Extension for Li-ion |     |

| BatteriesSC. Wang, GJ. Chen, and YH. Liu                                                        | 202 |

|                                                                                                 |     |

### **REGULAR PAPERS**

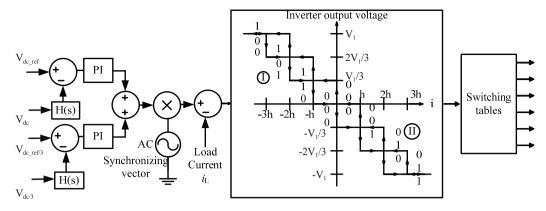

| Control of Neutral-Point Voltage in Three-Phase Four-Wire Three-Level NPC Inverter Based on | the            |

|---------------------------------------------------------------------------------------------|----------------|

| Disassembly of Zero Level                                                                   | <i>Xin</i> 213 |

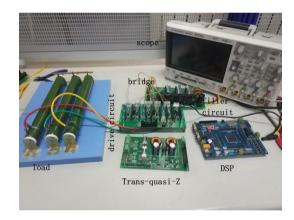

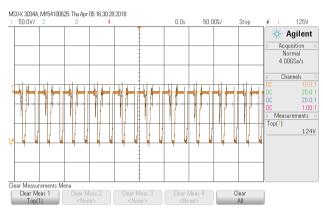

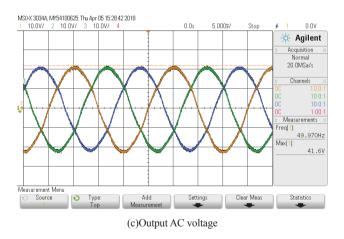

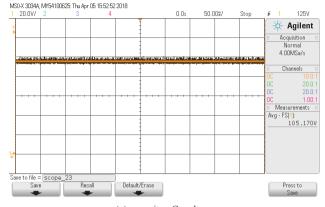

| Three Phase Trans-Quasi-Z-Source InverterX. Fang, B. Ma, G. Gao, and L.                     | <i>Gao</i> 223 |

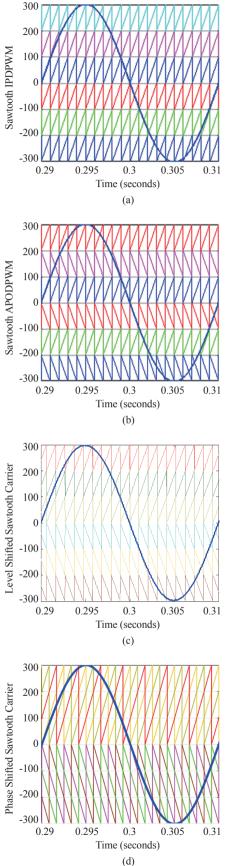

| Evaluation of Level-Shifted and Phase-Shifted PWM Schemes for Seven Level Single-Phase Pac  | ked            |

| U Cell InverterM. Tariq, M. Meraj, A. Azeem, A. I. Maswood, A. Iqbal, and B. Chokkalin,     | gam 232        |

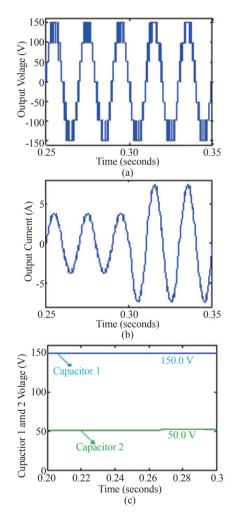

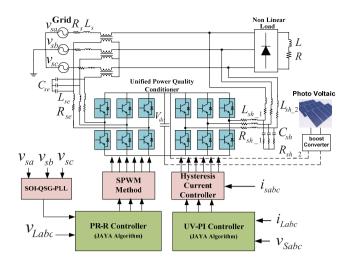

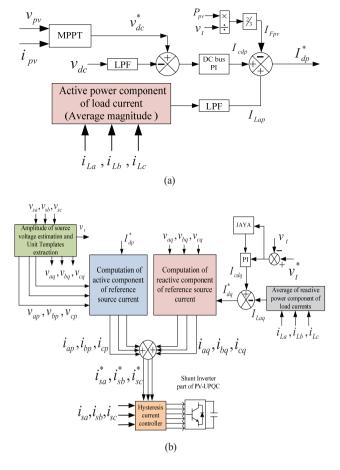

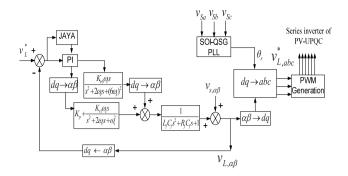

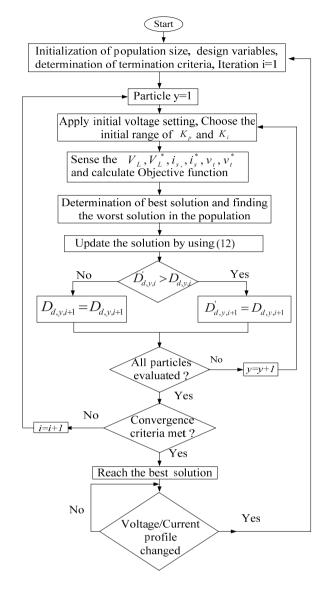

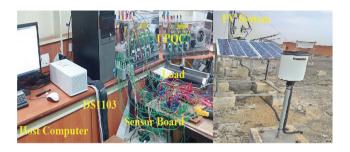

| Power Quality Improvement Utilizing PV Fed Unified Power Quality Conditioner Based on UV-PI | and            |

| PR-R ControllerS. K. Dash and P. K.                                                         | <i>Ray</i> 243 |

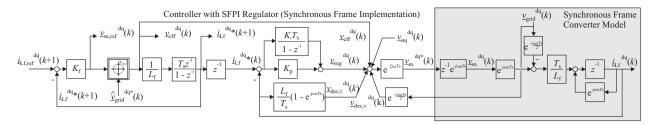

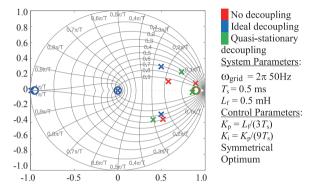

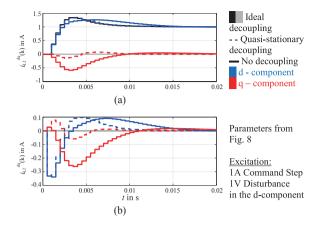

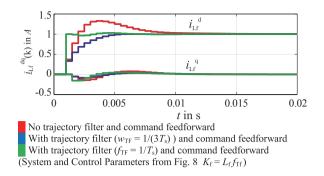

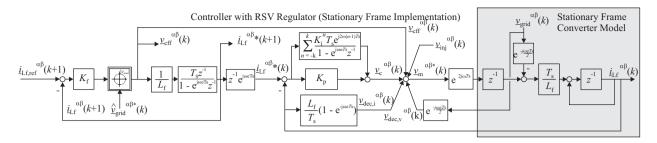

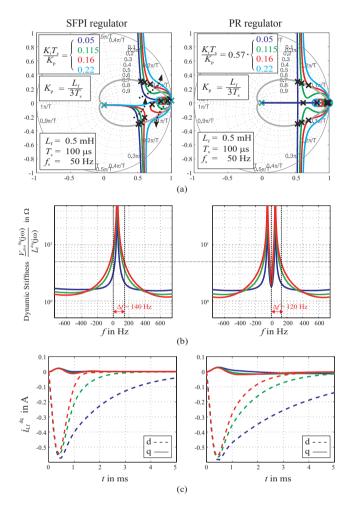

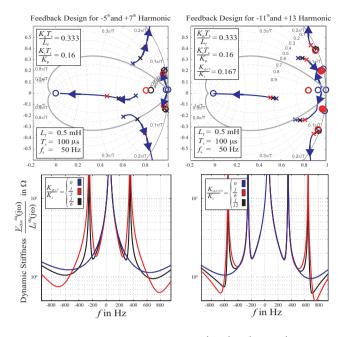

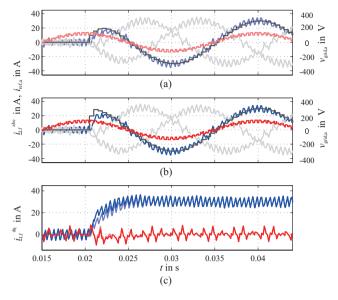

| Methodology for Analysis and Design of Discrete Time Current Controllers for Three-Phase P  | WM             |

| ConvertersC. H. van der Broeck, S. A. Richter, J. von Bloh, and R. W. De Don                | cker 254       |

### ANNOUNCEMENTS

# **CPSS TRANSACTIONS ON POWER ELECTRONICS AND APPLICATIONS**

CPSS Transactions on Power Electronics and Applications (CPSS TPEA) is sponsored and published by China Power Supply Society and technically co-sponsored by IEEE Power Electronics Society. It publishes original and high quality peer reviewed papers in the field of power electronics and its applications. With the goal of promoting the technology of power electronics including concepts, theory, modeling and control, analysis and simulation, emerging technology and applications, CPSS TPEA is expected to be a favorable platform to strengthen information exchange in this area. Interested authors are welcome to submit your papers via the Manuscript Central (https://mc03.manuscriptcentral.com/tpea-cpss) online submission system. You can find more information on our website: http://tpea.cpss.org.cn.

# **CPSS and PELS Joint Advisory Committee**

**Prof. Dehong Xu** Zhejiang University, China President of CPSS

**Prof. Jiaxin Han** The Institute of Seawater Desalination and Multipurpose Utilization, China Vice President of CPSS

**Prof. Jinjun Liu** Xi'an Jiaotong University, China Vice President of CPSS and Executive Vice President of PELS

### **Editor-in-Chief**

JINJUN LIU Xi'an Jiaotong University, China E-mail: jjliu@xjtu.edu.cn

#### **Editorial Office**

Tel: +86-22-27680796-18# Fax: +86-22-27687886 E-mail: tpea@cpss.org.cn Website: tpea.cpss.org.cn **Prof. Braham Ferreira** Delft University of Technology, Netherlands President of PELS

**Dr. Don Tan** Northrop Grumman Corporation, USA Past President of PELS

**Prof. Frede Blaabjerg** Aalborg University, Denmark Vice President of PELS

# Editorial for the Special Issue on Vehicle Electrification

LECTRIC, hybrid and fuel cell vehicles have attracted siginificant attention in the past decades due to the exhaustion of fossil fuel consumption and their environmental concerns. Electric vehicles use electronic subsystems-in comparison to conventional vehicles, which include electric machines, power electronics, electronic continuously variable transmissions (CVT), onboard chargers, and embedded powertrain controllers. Advanced energy storage systems, such as Li-ion batteries, ultra-capacitors, and fuel cells, together with intelligent energy management algorithms, are introduced in the next generation powertrains. In addition to these electrification components or subsystems, conventional internal combustion engines (ICE), mechanical and hydraulic systems may still present. As a result, the complexity of new powertrain designs and dependence on embedded software is a cause of concern to automotive research and development efforts. This leads to an increasing difficulty in predicting interactions among various vehicle components and systems. Therefore, the design and implementation of the mechanical and electrical components need to be considered carefully. In order to understand the difficulty and prospected challenge of the vehicle electrification, this Special Issue is a review of the state-of-art contributions and new discoveries in the field of power electronics and applications for the electric vehicle.

The Special Issue on Vehicle Electrification collected 4 papers on diverse topics, ranging from the overview to the new contributions on the power electronics for vehicle electrification. The first paper entitled "Parameter Identification of Capacitive Power Transfer System Based on Spectrum Analysis" as written by Chen Chen and his colleagues at the Institute of Electrical Engineering, Chinese Academy of Science (China). The multi-parameter identification method based on spectral information which using the rational fractional fitting algorithm and network synthesis theory is proposed in this paper. Some known-parameters are added to this method, the noise tolerance of the identification result is highly improved, resulting in z better accuracy. The experiment of the double-sided LC matched CPT system model with the vector network analyzer to collect the spectrum information of the circuit shows good results in effectively identifying the unknown parameters in the system model and achieving high accuracy.

The second paper on the "Adaptive DC-Link Voltage Control of LLC Resonant Converter" was proposed by Li-Chung Shih, Yi-Hua Liu and Yi-Feng Luo from National Taiwan University of Science and Technology, Taiwan. In this control technique, the DC-link voltage increases to compensate the voltage drop caused by load variation, which facilities the LLC resonant operates near the resonant frequency. Therefore, the frequency variation range can be reduced, and the efficiency is improved under different load conditions. Moreover, it also decreases the circulating energy and makes the optimal design of LLC converter possible. An experimental prototype was built to verify the feasibility of the controller.

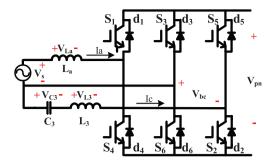

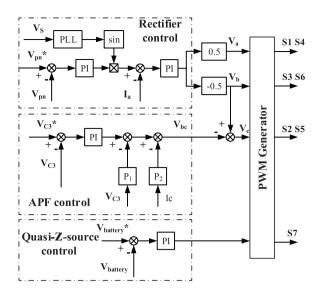

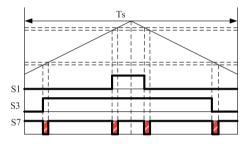

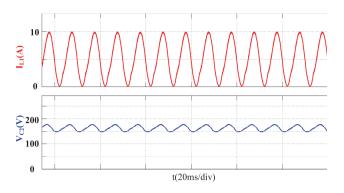

The third paper contributed by Tuopu Na and his colleagues from Harbin Institute of Technology (China) is the "Active Power Filter for Single-Phase Quasi-Z-Source Integrated On-Board Charger". The paper proposes an active power filter (APF) quasi-z-source single phase integrated on-board charger for EV application which can eliminate the second harmonic power on the DC-link. Compared with the conventional quasi-z-source network, this proposed topology only need a small capacitance and inductance, results in space and weight savings. This paper also discussed the design of the APF, and the experimental prototype was built to verify this design.

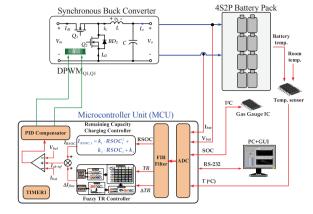

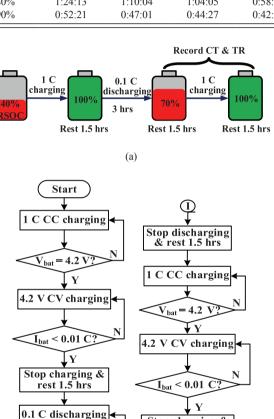

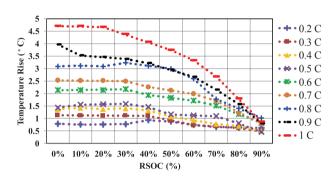

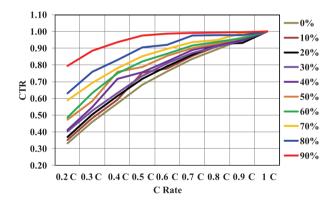

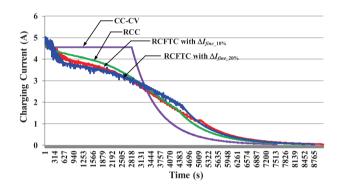

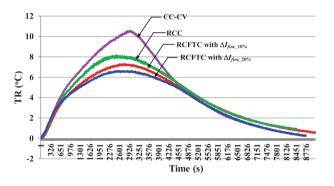

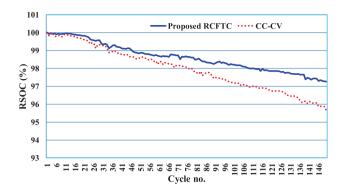

The last paper is the "Adaptive Charging Strategy with Temperature Rise Mitigation and Cycle Life Extension for Li-ion Batteries" from Shun-Chung Wang and his colleagues from Lunghwa University of Science and Technology, Taiwan. The digitally controlled Li-ion battery charger with an adaptive charging strategy has been employed in this paper. The devised charger can generate the desired charging profile depending on the battery SOC state and temperature variation. Accordingly, the proposed strategy remains the capacity charging with fuzzy temperature control approach that can avoid using the high C-rate current to charge the battery with high RSOC; thus, the phenomenon of the battery aging aggravation due to the extreme electrochemical stress can be subdued. The control strategy is implemented in the power stage of synchronous rectified buck converter for further conduction loss reduction. The GUI is also employed by a low-cost microcontroller and LabVIEW software. The experimental results show the significant improvement of the average temperature-rise, charging efficiency, estimated cycle life compared with the conventional CC-CV control strategy.

We would like to express our big appreciation to the industriousness and carefulness of the guest associate editors for this Special Issue in the selection of these high-quality papers from numerous submitted manuscripts in consideration for publication. We would like to appreciate the tremendous efforts of the expert reviewers who have provided invaluable, in-depth comments and suggestions to improve papers into the highest quality. We also would like to thank all the authors who have a great passion to achieve the best goal of their research for this Special Issue publication.

> Chris Mi Huang-Jen Chiu Guest Editors-in-Chief

**Chris Mi** is a fellow of IEEE and SAE, Professor and Chair of the Department of Electrical and Computer Engineering, and the Director of the US DOE funded GATE Center for Electric Drive Transportation at San Diego State University, San Diego, California, USA. He was previously a professor at the University of Michigan, Dearborn from 2001 to 2015. He received the B.S. and M.S. degrees from Northwestern Polytechnical University, Xi'an, China, and the Ph.D. degree from the University of Toronto, Toronto, Canada, all in electrical engineering. Previously he was an Electrical Engineer with General Electric Canada Inc. He was the President and the Chief Technical Officer of 1Power Solutions, Inc. from 2008 to 2011. He is the Co-Founder of SNC Technology.

His research interests are in electric and hybrid vehicles. He has taught tutorials and seminars on the subject of HEVs/PHEVs for the Society of Automotive Engineers (SAE), the IEEE, workshops sponsored by the National Science Foundation (NSF), and the National Society of Professional Engineers. He has delivered courses to major automotive OEMs and suppliers, including GM, Ford, Chrysler, Honda, Hyundai, Tyco Electronics, A&D Technology, Johnson Controls, Quantum Technology, Delphi, and the European Ph.D. School. He has offered tutorials in many countries, including the U.S., China, Korea, Singapore, Italy, France, and Mexico. He has published more than

250 articles and delivered 100 invited talks and keynote speeches and as a panelist in major IEEE and SAE conferences. Dr. Mi is the recipient of "Distinguished Teaching Award" and "Distinguished Research Award" of University of Michigan Dearborn. He is a recipient of the 2007 IEEE Region 4 "Outstanding Engineer Award," "IEEE Southeastern Michigan Section Outstanding Professional Award." and the "SAE Environmental Excellence in Transportation (E2T) Award." He was also a recipient of the National Innovation Award and the Government Special Allowance Award from the

China Central Government. He received two Best Paper Awards from IEEE Transactions on Power Electronics.

Dr. Mi was the Chair (2008-2009) and Vice Chair (2006-2007) of the IEEE Southeastern Michigan Section. Dr. Mi was the general Chair of the 5th IEEE Vehicle Power and Propulsion Conference held in Dearborn, Michigan, USA in September 6-11, 2009. Dr. Mi is one of the three Area Editors of *IEEE Transactions on Vehicular Technology*, Associate Editor of *IEEE Transactions on Power Electronics*, Associate Editor of *IEEE Transactions on Industry Applications*. He served on the review panel for the NSF, the U.S. Department of Energy (2007–2010), the Natural Sciences and Engineering Research Council of Canada (2010), Hong Kong Research Grants Council, French Centre National de la Recherche Scientifique, Agency for Innovation by Science and Technology in Flanders (Belgium), and the Danish Research Council. He is the topic chair for the 2011 IEEE International Future Energy Challenge, and the General Chair for the 2013 IEEE International Future Energy Challenge. Dr. Chris Mi is a Distinguished Lecturer (DL) of the IEEE Vehicular Technology Society.

He is Guest Editor-in-Chief of *IEEE Journal of Emerging and Selected Topics in Power Electronics – Special Issue on WPT*, Guest Co-Editor-in-Chief of *IEEE Transactions on Power Electronics Special Issue on WPT*, Guest Editor of *IEEE Transactions on Industrial Electronics – Special Issue on Dynamic Sireless Power Transfer*, and steering committee member of the IEEE Transportation Electrification Conference (ITEC- Asian). He is Program Chair or General Chair of a number of international conferences, including Workshop on Wireless Power Transfer (WoW), IEEE International Electric Vehicle Conference (IEVC), and IEEE International Transportation Electrification Conference – Asia-Pacific. He is also the chair for the IEEE Future Direction's Transportation Electrification Initiative (TEI) e-Learning Committee and developed an e-learning module on wireless power transfer.

Huang-Jen Chiu has been with the Department of Electronic and Computer Engineering, National Taiwan University of Scienceand Technology, Taipei, Taiwan, where he is a Distinguished Professor and the Director of Center for Power Electronic Technologies, now. His research interests include high efficiency/high power density bidirectional DC/DC converters, PFC topologies, PV inverters, and DSP control in renewable energy applications.

His work brought him several distinctive awards including the Young Researcher Award in 2004 from the Ministry of Science and Technology, Taiwan, the Outstanding Teaching Award in 2009 and 2017, the Excellent Research Award in 2009 and 2011, the Excellent Academic-industry collaboration Award in 2015 and 2017 from the NTUST, the Y. Z. Hsu Scientific Paper Award in 2010 and Google Little Box Academic Awards. His student teams won the grand prize of the IEEE International Future Energy Challenge (IFEC) in 2013 and 2015, respectively. Dr. Chiu is an IEEE senior member and serves as an Associate Editor of the *IEEE Transactions on Industry Applications* and an Associate Editor of the *IEEE Transactions on Circuits and Systems Part II: Express Letters (TCAS-*

*II).* He served as the Taipei Chair of IEEE Industrial Electronics Society (2015-2016), the General Co-chair of 2017 IEEE International Future Energy Electronics Conference (IFEEC 2017-ECCE Asia), the Program Chair of 2015 IEEE International Future Energy Electronics Conference (IFEEC 2015), the Topic Co-Chair of 2016 International Future Energy Challenge (IFEC 2016) and the Secretary of IEEE PELS/ IES Taipei Joint Chapter during 2010-2014. Dr. Chiu is a Fellow of the Institute of Engineering and Technology (IET) and selected as the Distinguished Lecture of IEEE Power Electronics Society (2017-2018).

# Parameter Identification of Capacitive Power Transfer System Based on Spectrum Analysis

Chen Chen, Chenhui Li, Chenglin Liao, and Lifang Wang

Abstract—Capacitive power transfer (CPT) technology is a newly emerging research focus for EV charging applications. Due to the absence of eddy current loss and light weight of the capacitive coupling metal plates, CPT technology is considered to be a promising alternative to the inductive power transfer (IPT) technology. However, the parameter identification of the CPT system has not been well studied. In this paper, a multi-parameter identification method based on spectral information is proposed, which based on rational fractional fitting algorithm and network synthesis theory. By adding some known parameters to this method, the parameter identification algorithm under constraint is proposed to improve the noise tolerance of the identification results, and at the same time, it can also have better identification accuracy. The experimental results show that the parameter identification algorithm based on spectrum information can effectively identify the parameters of the circuit model of the CPT system, and the identification accuracy is less than 10%.

*Index Terms*—Capacitive power transfer, frequency spectrum, network synthesis, noise tolerance, parameter identification.

#### I. INTRODUCTION

CAPACITIVE power transfer (CPT) [1], [2] technology transfers energy through the electric field between the air gap. This idea can be traced back to Nikola Tesla's bold idea of transferring wireless energy through the capacitance of the ionosphere. Recently, with the increase of the power capacity of the CPT system, it has become a new research focus in the field of wireless charging for electric vehicles.

CPT technology has several unique advantages against the widely-used inductive power transfer (IPT) technology. First, the electric fields do not generate eddy current in the metal material nearby as the magnetic fields do. Besides, the capacitive coupling is usually composed of several conductive plate pairs with no ferrite required, so the coupling part of the CPT is in low cost and light in weight [3]. With these advantages, CPT is considered to be a promising technology in wireless EV charging [4].

Jiejian Dai proposed a design composed of conducting foil at the rear of the EV and a foam-based bumper at the charging station. This technique allows for simple mechanical implementation and avoids the pitfalls associated with alignment and air gap maintenance usually encountered with CPT systems [5].

The double-sided LCLC CPT system proposed by Lu is a breakthrough in designs of high-power long-distance CPT system, and this prototype system can transfer 2.4 kW power at a distance of 150 mm. This work provides a complete design of CPT system for EV charging which reaches a DC-to-DC efficiency of over 90% and works on a relatively low frequency of 1 MHz [6].

Lu also refined LCLC compensation to CLLC compensation, which reduces the inductance needed for compensation [7]. A simpler LC compensation is also analyzed comparing with the LCLC topology which seemed to be more feasible as it has less components to tune [8]. Due to its simplicity, it is more likely to be realized on EV charging scenario [9].

However, during the wireless charging process of EV, wireless power transfer (WPT) system often needs to work under different coupling conditions due to the uncertainty of the placement position and external conditions of the coupling device. Therefore, the same transmitter-end device may need to have the ability to supply power to multiple receiver devices with different parameters. At present, many parameter identification methods have been developed in inductively coupled power transfer (ICPT) systems, but there are few studies on the parameter identification of the CPT system [10].

In the parameter identification study of ICPT system, most of the identification algorithms are only for a single unknown parameter under the premise of known circuit model parameters. Reference [11] is based on the principle of energy conservation, using the circuit model of the matching circuit to derive the relationship between the voltage and current at the output of the inverter and the load at the receiving end, so as to realize parameter identification of the load at the output. The reference [12] realizes the parameter identification of the output load by measuring the decay speed of the circuit's free oscillation.

For the case where the coupled inductance and the load resistance are unknown, the reference [12] uses the standard load resistance at the output end. First, the coupled inductor is identified under the operating condition of the standard load, and then the actual load resistance is performed under the condition that the coupled inductor identification value is obtained, thereby achieving multi-parameter identification.

In the ICPT system, the change of the coupled inductance does not affect the phase of the reflected impedance. The reference [13] measures the voltage and current output from the inverter, and uses the phase of the reflected impedance to identify the load resistance, and then uses the reflection im-

Manuscript received July 26, 2018. (Corresponding author: Chenglin Liao.)

The authors are with the Key Laboratory of Power Electronics and Electric Drive, Institute of Electrical Engineering, Chinese Academy of Sciences, Beijing 100190, China (e-mail: chenchen@mail.iee.ac.cn; lichenhui@mail.iee. ac.cn; liaocl@mail.iee.ac.cn; wlf@mail.iee.ac.cn).

Digital Object Identifier 10.24295/CPSSTPEA.2018.00017

pedance amplitude to identify the coupled inductance. This realizes the identification of coupled inductance and output load.

The identification methods used in the above ICPT system often rely on accurate measurement of known parameters of the circuit or directly interpolate fitting results directly from the experimental results. Each identification method is often designed independently according to a specific identification target, and the unknown parameter is also limited to the coupled inductance and the load resistance.

At present, the parameter identification of the CPT system is not well study, this is due to its higher operating frequency and higher requirements on the sampling circuits. On the one hand, there is a coupling relationship between the coupling capacitance and the reflected impedance of CPT, which leads us to be unable to use the method mentioned in reference [13]. On the other hand, the resonant operating frequency of the capacitive system is narrower, and its working state is greatly affected by the matching parameters, if the circuit parameters cannot be accurately measured, it is difficult to obtain good estimation accuracy by using the method described in the reference [12].

Therefore, this paper proposes a more general parameter identification algorithm for the CPT system. Since the result obtained by directly using the driving-point function is very sensitive to noise, in order to improve the applicability of parameter identification, the partial loss resistance and matching circuit component parameters in the model circuit are taken as known values, and by adding these known values as constraints to the identification system model, the noise tolerance of the algorithm can be improved.

#### II. PARAMETER IDENTIFICATION METHOD USING FREQUENCY SPECTRUM INFORMATION

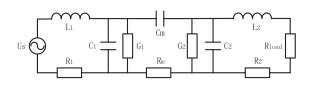

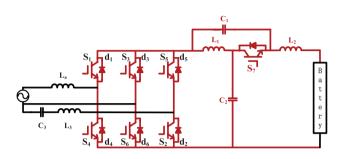

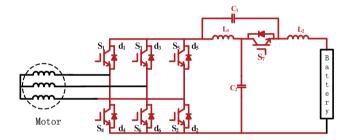

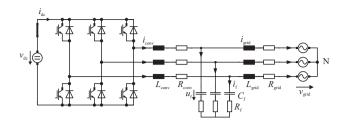

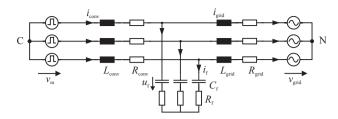

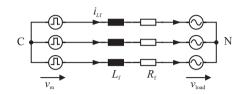

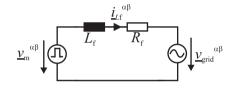

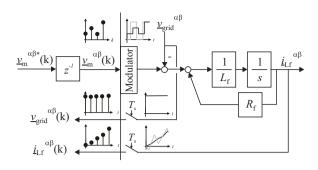

The circuit model of CPT system is shown in Fig. 1, where  $L_1, C_1, L_2, C_2$  respectively for the transmitter and receiver matching circuit inductance and capacitance, Cm for the coupling capacitor, R<sub>load</sub> for the load resistance. By analyzing its circuit model, we can know that when the output load is stable, the system can be seen as a single-port network driven by the inverter output, and the internal components of the network are lumped-parameter linear components. Therefore, the problem of parameter identification for CPT systems can be abstracted as a parameter identification problem for a single-port network. According to the circuit network theory, for a linear single-port network, its external characteristics are fully determined by the driving-point function of the port, the driving-point function can select admittance functions or impedance functions [14]. Here, taking the admittance function as an example, the driving-point function can be expressed in a rational fractional form:

$$Y(\mathbf{s}) = \frac{I_{in}(\mathbf{s})}{U_{in}(\mathbf{s})} = \frac{\sum a_i s^i}{\sum b_j s^j}$$

(1)

Fig. 1. Circuit model of CPT system.

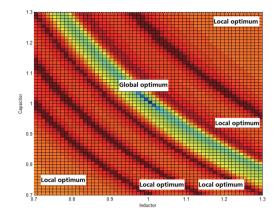

Fig. 2. Solution space map.

where,  $I_{in}$  and  $U_{in}$  represent the input current and voltage of the network port respectively, the parameters a and b in the above equation are real numbers, and the order of the numerator and denominator is determined by the topology and component parameters of the circuit.

Next, we need to fit the finite discrete points you have collected, it can generally be assumed that the noise distribution of the sampled values follows a normal distribution, and the sum of the squares of the fitting errors can be used as a criterion.

Since the fitting function is a nonlinear function, if the network is fitted directly using the second-order error minimum principle, the nonlinear least squares problem will be obtained.

$$\min \left\| \tilde{Y}(j\omega_i) - Y(j\omega_i) \right\|_2$$

(2)

where  $\tilde{Y}(s) = \frac{\sum k_i s^i}{\sum d_j s^j}$  means the fitted function,  $k_i$  and  $d_j$  are the undetermined coefficients of the function.

Directly using the sum of squared errors as an optimization index, the optimization problem is that the function is not non-convex, and the fitting error has multiple local optima in the search space, as shown in Fig. 2. Therefore, directly using ordinary nonlinear optimization algorithms, such as the Levenberg-Marquardt method or the trust region method, it is difficult to converge to the optimal value for nonlinear optimization.

In order to solve the problem of a locally optimal solution of nonlinear least squares fitting algorithm in rational fractional fitting, we use the Vector Fitting algorithm [15] to solve the nonlinear least squares problem. First, transform  $\tilde{Y}(s)$  in (2) into a fractional representation by partial fractionation,

$$\tilde{Y}(s) = \frac{\sum(s-z_i)}{\sum(s-p_j)}$$

(3)

then multiplied by the weight  $\frac{\sum(s-p_i)}{\sum(s-\tilde{p}_i)}$  to get the linearized least squares problem, in the formula,  $z_i$  and  $p_j$  represent the zero point and the pole, respectively, and  $\tilde{p}_i$  is expressed as the estimated pole.

$$\min \left\| (\sigma \tilde{Y})(j\omega_i) - Y(j\omega_i)\sigma(j\omega_i) \right\|_{2}$$

(4)

where  $(\sigma \tilde{Y})(s) = \sum_{i=1}^{\infty} (s-z_i), \sigma(s) = \sum_{i=1}^{\infty} (s-p_i)$ . Therefore, the Vector Fitting algorithm can be used to fit the driving-point function. After using the Vector Fitting algorithm to fit the system's driving-point function, we need to find actual circuit parameters from the function expression. In the CPT system, since the topology of the matching circuit is mostly a ladder network structure, the Cauer synthesis method [16] can be used to get the synthesis of the circuit network. The driving-point function expression of the system regarding the circuit component is obtained as follows:

$$Y(s) = \frac{1}{L_1 s + R_1 + \frac{1}{C_1 s + G_1 + \frac{1}{C_m s} + R_m + \frac{1}{C_2 s + G_2 + \frac{1}{L_2 s + R_2 + R_{load}}}}$$

(5)

Expand (5) to get the admittance function expression of the (1), the highest order of the obtained molecular terms is 4 times, and the denominator term is 5 times, as shown in (6).

$$Y(s) = \frac{a_4 s^4 + a_3 s^3 + a_2 s^2 + a_1 s + a_0}{b_5 s^5 + b_4 s^4 + b_3 s^3 + b_2 s^2 + b_1 s + b_0}$$

(6)

Using Vector Fitting algorithm as a rational fractional fitting algorithm, Cauer synthesis method is used as a network synthesis method to identify the parameters in the circuit, then the correlation coefficients in (6) can be obtain derived, which means that the effective parameters of the actual circuit are obtained.

To sum up, the input parameter identification of the CPT system consists of two parts:

- 1) Fitting of driving-point function. By applying the excitation and measuring the system response, the external characteristics of the network in the form of the driving-point function are obtained by fitting.

- 2) Integration of network parameters. According to the expression of the driving-point function, the realization of the circuit network in the corresponding topology is obtained, take this implementation value as an estimate of the parameter.

Through simulation, the parameter identification results under noiseless sampling are shown in TABLE I.

According to the simulation experiment under the noise, if

TABLE I NOISELESS LOSSY MODEL IDENTIFICATION RESULTS

| Circuit Parameters                  | Loss Model<br>Identification Results<br>When $R_m = 100 \Omega$ | Model Parameters |

|-------------------------------------|-----------------------------------------------------------------|------------------|

| $L_1(H)$                            | 8.2240e-005                                                     | 82.24 uH         |

| $\mathrm{R}_{1}\left(\Omega ight)$  | 3.4401                                                          | 3.44 Ω           |

| $C_1(F)$                            | 2.8800e-010                                                     | 288 pF           |

| $G_{1}(S)$                          | 1.0000e-005                                                     | 10e-6S           |

| $C_{m}(F)$                          | 1.9995e-011                                                     | 20 pF            |

| $R_{m}\left( \Omega  ight)$         | 1.0003e+002                                                     | 100 Ω            |

| $C_2(F)$                            | 2.8801e-010                                                     | 288 pF           |

| $G_{2}(S)$                          | 9.9966e-006                                                     | 10e-6S           |

| $L_2$ (H)                           | 8.2277e-005                                                     | 82.24 uH         |

| $R_{load}+R_{2}\left( \Omega ight)$ | 36.5561                                                         | 36.54 Ω          |

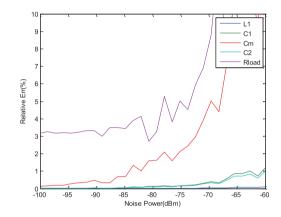

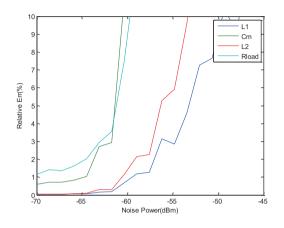

Fig. 3. Identification error of partial lossless model under different sampling noise power.

we want to achieve 10% estimation error in the experiment, the sampled value noise needs to be higher than 70dBm, as shown in Fig. 3, where shows the relationship between the error rate of the identification parameters and the noise. It can be clearly seen from the Fig. 3 that the sensitivity of Cm and  $R_{load}$  to noise is higher than other parameters, and once the noise exceeds 70dBm, the identification error rate of  $R_{load}$  will exceed 10%.

#### III. PARAMETER IDENTIFICATION ALGORITHM UNDER CONSTRAINTS

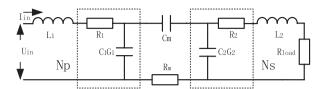

Taking a CPT system with double-sided LC matching as an example, assuming that the inductance L1, L2, coupling capacitance Cm, and load resistance  $R_{load}$  in the circuit parameters are unknown, the circuit model is shown in Fig. 4. The transmitter resistor and capacitor parameters are known to form a two-port circuit Np, the receiver resistor and capacitor parameters are known to form a two-port circuit Ns.

In this algorithm, the unknown variables are modeled in a two-port network, the circuit is decomposed according to the unknown part and the known part, and the unknown parts are separately solved in an iterative manner, and at the same time, the rational fractional fitting method is used, the fol-

Fig. 4. The parameter identification model under the constraint of double-sided LC matched CPT system.

Fig. 5. Identification error of identification algorithm under constraint with different sampling noise power.

lowing fitting algorithm can be designed.

- 1) Given the initial value of load resistance and coupling capacitance  $\tilde{R}_{load}$ ,  $\tilde{C}_m$  and the inductance  $\tilde{l}_1$ ,  $\tilde{l}_2$  at both ends.

- 2) Taking  $\tilde{R}_{load}$ ,  $\tilde{C}_m$  and  $\tilde{l}_2$  as known variables, the back-end circuit of the inductor  $l_1$  is known, and the inductor  $l_1$  is fitted and solved under the back-end constraint as a new front-end inductance estimated value  $\tilde{l}_1 = l_1$ .

- 3) Taking  $\tilde{R}_{load}$ ,  $\tilde{l}_1$  and  $\tilde{l}_2$  as known variables, the front and back-end circuits of the coupling capacitor  $C_m$  are known, and the coupling capacitor  $C_m$  is fitted and solved under the front and rear end constraints as a new coupling capacitor estimate  $\tilde{C}_m = C_m$ .

- 4) Taking  $\tilde{l}_1$  and  $\tilde{C}_m$  as known variables, the front-end circuits of the inductor and load resistors  $l_2$  and  $R_{load}$  are known, and the inductance and load resistance  $l_2$  and  $R_{load}$  are fitted and solved under the front-end constraints as a new coupling capacitor estimate  $\tilde{l}_2 = l_2$ ,  $\tilde{R}_{load} = R_{load}$ .

- 5) If the fitting error is less than the threshold, it ends, otherwise, it returns to 2).

In the above algorithm, by modeling the unknown variables in the form of a two-port network, the circuit is decomposed according to the position part and the known part, and the unknown parts are separately solved in the form of iterations.

Though the simulation experiment under the noise, we can see that if we want to achieve 10% estimation error in the experiment, the sample value noise needs to be higher than 60dBm, as shown in Fig. 5, compared to the identification algorithm based on spectrum information without constraint, the new algorithm can reduce signal-to-noise ratio require-

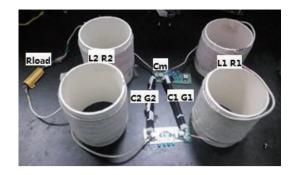

Fig. 6. Double-sided LC matched CPT system model circuit physical map.

TABLE II Parameter Identification Effect of Parameter Identification Algorithm on Model Physical Circuit

| Circuit Parameters | Constraint Model<br>Identification Results | Component<br>Measurement |

|--------------------|--------------------------------------------|--------------------------|

| $L_1$              | 7.6887e-005                                | 77.1773 uH               |

| $R_1$              | -                                          | 3.6928 Ω                 |

| $C_1$              | -                                          | 265.7394 pF              |

| $G_1$              | -                                          | 5e-6S                    |

| Cm                 | 2.0501e-011                                | 20 pF                    |

| R <sub>m</sub>     | -                                          | -                        |

| $C_2$              | -                                          | 252.2711 pF              |

| $G_2$              | -                                          | 6e-6                     |

| $L_2$              | 7.8756e-005                                | 78.8456 uH               |

| $R_2$              | -                                          | 3.43 Ω                   |

| R <sub>load</sub>  | 20.9163                                    | 20 Ω                     |

ments of approximately 10 dB.

-

### IV. MODEL CIRCUIT PARAMETER IDENTIFICATION EXPERIMENT

In order to verify the applicability of the algorithm in the actual circuit parameter identification. According to the circuit model of the double-sided LC matching coupling capacitor shown in Fig. 1, the circuit physical map is shown in Fig. 6. The electronic system is used to build the circuit system and the equivalent model physical circuit is made.

A hollow flat wound coil made of 600 strands x 0.1 mm Litz wire is used in the circuit as an inductor in the matching circuit. A plurality of EPCOS film capacitors with a capacitance of 1nF are used in series as the capacitance in the matching circuit, and the coupling capacitance is replaced with a 15pF ceramic capacitor. The actual parameters of the above components were measured using an Agilent E4980A LCR digital bridge, and the actual parameters of the system were as shown in the measured values of the components in TABLE II.

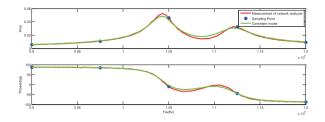

Comparing the constraint model fitting results with the measurement results, the constraint model is constrained by the measured values of the known components, and the identification results are close to the actual circuit parameters, as shown in Fig. 7, where the red line is the result of the vector network analyzer measurement, while the green line

Fig. 7. Comparison of the results of the constraint model fitting and the measurement results.

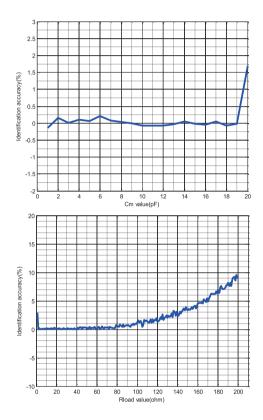

Fig. 8. (a) Relationship between coupling capacitance change and identification accuracy. (b) Relationship between load resistance change and identification accuracy.

is the result of fitting the five blue sampling points using our proposed identification algorithm. It can also be seen from TABLE II that the constraint model can accurately identify the value of the circuit component and the identification accuracy is less than 10%. At the same time, the noise is set to 65dBm. By changing the value of the load resistance and keeping the other parameters of the circuit unchanged, a curve about the load value and the identification accuracy can be obtained, as shown in Fig. 8(b). Keeping the noise at 65dBm, by changing the value of the coupling capacitor and keeping the other parameters of the circuit unchanged, a curve about the coupling capacitance value and the identification accuracy can be obtained, as shown in Fig. 8(b). Keeping the noise at 65dBm, by changing the value of the coupling capacitor and keeping the other parameters of the circuit unchanged, a curve about the coupling capacitance value and the identification accuracy can be obtained, as shown in Fig. 8(a).

#### V. CONCLUSION

This paper proposes a method of parameter identification based on spectrum information, by adding known parameters of the circuit, the accuracy and noise tolerance of the identification algorithm are improved. In order to verify the proposed algorithm, this paper firsts builds a double-sided LC matched CPT system model physical circuit as shown in Fig. 6. Then, the vector network analyzer is used to collect the spectrum information of the circuit, and the parameter identification algorithm is applied on it. The final result verifies that the parameter identification algorithm based on spectrum information can achieve good results, which not only can effectively identify the unknown parameters in the system model, but also achieve the identification result with less than 10% accuracy.

#### REFERENCES

- J. T. Boys and G. A. Covic, "The inductive power transfer story at the university of auckland," *IEEE Circuits and Systems Magazine*, vol. 15, no. 2, pp. 6-27, May 2015.

- [2] A. Karalis, J. D. Joannopoulos, and M. Soljačić, "Efficient wireless non-radiative mid-range energy transfer," *Annals of Physics*, vol. 323, no. 1, pp. 34-48, Jan. 2008.

- [3] C. H. Li, X. M. zhao, C. L. Liao, and L. F. Wang, "A graphical analysis on compensation designs of large-gap CPT systems for EV charging applications," *CES Transactions on Electrical Machines and Systems*, vol. 3, no. 2, pp. 232-242, Jul. 2018.

- [4] C. Mi, "High power capacitive power transfer for electric vehicle charging applications," in 6th International Conference on Power Electronics Systems and Applications (PESA), 2015, pp. 1-4.

- [5] J. Dai and D. C. Ludois, "Wireless electric vehicle charging via capacitive power transfer through a conformal bumper," in 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), 2015, pp. 3307-3313.

- [6] F. Lu, H. Zhang, H. Hofmann, and C. Mi, "A double-sided LCLC-compensated capacitive power transfer system for electric vehicle charging," *IEEE Transactions on Power Electronics*, vol. 30, no. 11, pp. 6011-6014, Nov. 2015.

- [7] F. Lu, H. Zhang, H. Hofmann, and C. Mi, "A CLLC-compensated high power and large air-gap capacitive power transfer system for electric vehicle charging applications," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), 2016, pp. 1721-1725.

- [8] F. Lu, H. Zhang, H. Hofmann, and C. Mi, "A double-sided LC-compensation circuit for loosely coupled capacitive power transfer," *IEEE Transactions on Power Electronics*, vol. 30, no. 2, pp. 1633-1643, Feb. 2018.

- [9] F. Lu, H. Zhang, and C Mi, "A two-plate capacitive wireless power transfer system for electric vehicle charging applications," *IEEE Transactions on Power Electronics*, vol. 33, no. 2, pp. 964-969, Feb. 2018.

- [10] H. Y. Zhang, "Load and mutual inductance identification method of ICPT system based on switching capacitors," Chongqing University, 2015.

- [11] X. Dai, Y. Sun, and C. Tang, "Dynamic parameters identification method for inductively coupled power transfer system," *IEEE International Conference on Sustainable Energy Technologies*, Dec. 2010.

- [12] Z. H. Wang, Y. P. Li, and Y. Sun, "Load detection model of voltage-fed inductive power transfer system," *IEEE Transactions on Power Electronics*, vol. 28, no. 11, pp. 5233-5243, Nov. 2013.

- [13] J. F. Li, C. L. Liao, and L. F. Wang, "Decoupling method of maximum efficiency and transferring power for electric vehicle wireless charging system via LCCL circuit," *Transactions of China Electrotechnical Society*, pp. 199-203, 2010.

- [14] V. Belevitch, "Summary of the history of circuit theory," *Proceeding of the Ire*, vol. 50, no. 5, pp.848-855, May 1962.

- [15] B. Gustavsen and A. Semlyen, "Rational approximation of frequency domain responses by vector fitting," *IEEE Transactions on Power Delivery*, vol. 14, no. 3, pp. 1052-1061, Jul. 1999.

- [16] W. Cauer, "Die Verwirklichung von Wechselstromwiderständen vor-

geschriebener Frequenzabhängigkeit," Archiv Für Elektrotechnik, vol. 17, no. 4, pp. 355-388, Apr. 1926.

Chen Chen received the B.E. degree in automation from Tianjin Polytechnic University, Tianjin, China, in 2016. He then completed studies in power electronics and electric drives at the University of Chinese Academy of Sciences, Beijing, China. He is currently working towards the M. S. degree in power electronics and electric drives at the Institute of Electrical Engineering, Chinese Academy of Sciences, Beijing, China. His research topic focuses on wireless power transfer for electric vehicle

charging and aided inertial navigation system for vehicles.

Chenglin Liao received the Ph.D. degree in power machinery and engineering from Beijing Institute of Technology, Beijing, China, in 2001. He then spent two years as a Postdoctoral Researcher with Tsinghua University, Beijing, China. He is currently the Deputy Director of the Department of Vehicle Energy System and Control Technology, Institute of Electrical Engineering, Chinese Academy of Sciences, Beijing, China. He had been involved in research on battery management systems, vehicle

control, and wireless charging systems for electric vehicles for the past nine years at the Institute of Electrical Engineering. His research interests include the development of high-power wireless charging systems for commercial electric vehicles.

Lifang Wang received the Ph.D. degree in automobile engineering from Jilin University, Jilin, China, in 1997. She then joined the Institute of Electrical Engineering, Chinese Academy of Sciences, Beijing, China. During the Chinese 10th five-year plan (2001–2005), she was a member of the National Specialist Group of the Key Special Electric Vehicle Project of the National 863 Program, and she was the Head of the 863 Special EV Project Office. She is currently the Director of the

Department of Vehicle Energy System and Control Technology, Institute of Electrical Engineering, Chinese Academy of Sciences, Beijing, China. She is also the Vice Director of the Key Laboratory of Power Electronics and Electric Drives, Chinese Academy of Sciences. Her research interests include electric vehicle control systems, EV battery management systems, wireless charging systems for EVs, electromagnetic compatibility and smart electricity use. She has directed more than 15 projects in these fields and has published more than 60 papers and 30 patents.

**Chenhui Li** received the B.E. degree in automation from Tsinghua University, Beijing, China, in 2015. He received the M.S. degree in power electronics and electric drives at the Institute of Electrical Engineering, Chinese Academy of Sciences, Beijing, China, in 2018. His research topic focuses on wireless power transfer for electric vehicle charging. He is working on the high power capacitive power transfer through air-gap distance and measurement technology of the wireless power transfer system.

# Adaptive DC-Link Voltage Control of LLC Resonant Converter

Li-Chung Shih, Yi-Hua Liu, and Yi-Feng Luo

*Abstract*—In this study, an adaptive DC-link voltage control of a two-stage switching power supply with LLC resonant converter is proposed. With this control method, the frequency variation range can be reduced and the conversion efficiency under different load conditions can be improved compared with the conventional variable frequency control technique. By operating the LLC resonant converter near its resonant frequency, circulating loss as well as the conduction loss can be reduced and optimal design of LLC resonant converter can be made possible. Moreover, no additional auxiliary circuits are required for the proposed method. The operational principle of the proposed control scheme is verified with a 350 W prototyping circuit. The switching-frequency-variation range is reduced from 12 to 4 kHz and the efficiency is improved from 89.4 % to 90.2 % at full load.

*Index Terms*—Adaptive DC-link control, LLC resonant converter, two-stage switching power supply.

#### I. INTRODUCTION

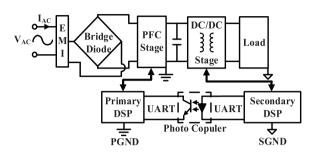

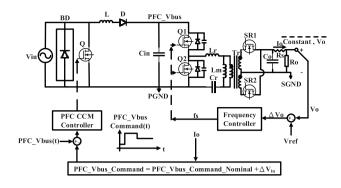

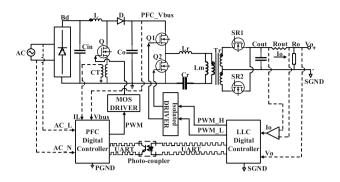

WITH the prevalence of the Internet and advancements in telecommunication technology, demand for power supply fields, such as server and telecom power supplies, has increased. Additionally, consumers have high requirements for power supply efficiency, volume, power density, and reliability [1]-[3]. Regarding the application of server and telecom power supplies, two-stage switching power supply (SPS) remains the mainstream architecture [4], [5]. In addition, two-stage SPS can also be employed in plug-in electrical vehicle (PEV) applications. Power factor correction (PFC) is usually the first stage of two-stage SPS, allowing the input current to become sinusoidal and in phase with the input voltage to increase the usage of mains electricity. The PFC stage usually utilizes a typical boost converter architecture that converts alternating current (AC) mains electricity to high-voltage direct current (DC). The second stage utilizes a DC-DC converter architecture to provide isolation as well as a stable output voltage. For two-stage SPS, digital signal controllers have increasingly been employed because of advancements in their functionalities. The block diagram for two-stage digital SPS is shown in Fig. 1.

Because most conventional DC-DC converters do not possess soft switching mechanisms [6], power supply efficiency is

Fig. 1. Block diagram of a two-stage digital SPS.

difficult to improve. Hence, current DC-DC converters typically use the phase shift full bridge (PSFB) converter or LLC resonant converter, which has soft switching characteristics. PSFB converters can achieve zero voltage switching (ZVS) and are suitable for medium- and high-power applications; therefore, they are often used in the DC-DC converters of server, telecom or PEV power supply systems. Compared with conventional full bridge converters, PSFB converters have higher efficiency; however, PSFB converters exhibit problems such as difficulty in achieving ZVS at light load, duty cycle loss, circulating-current loss, and the parasitic ringing phenomenon [7]-[10].

Compared with PSFB converters, LLC resonant converters can not only achieve ZVS on the primary side but also attain zero current switching (ZCS) on the secondary side. In addition, problems related to the circulating current on the primary side of the LLC resonant converter are less severe. Thus, LLC resonant converters are more efficient than PSFB converters and have gradually become more prevalent for DC-DC converter applications. However, LLC resonant converters possess deficiencies. Generally, the optimal performance of an LLC resonant converter occurs when the switching frequency equals the resonant frequency [11]-[16]. However, this is difficult to achieve without adding mechanisms such as changes to the resonant tank parameters [12], [13] or modulation of the LLC resonant converter input voltage [14]-[16]. In addition, the LLC resonant converter relies on a frequency control mechanism to achieve voltage regulation. In conditions of improper design or applications where a wide input/output range is required [17]-[20], the switching frequency of LLC resonant converter may vary excessively, causing inefficiency and even leading to problems in designing magnetic components.

Numerous studies have adopted measures to enhance the overall efficiency of LLC resonant converters. A dual-transformer strategy was utilized in [19] to handle relatively wide input voltage ranges. Compared with the conventional LLC resonant converter, this design developed more operating modes, such as the increased flexibility to minimize the magnetizing

Manuscript received July 30, 2018. This work was financially supported by the Taiwan Building Technology Center from The Featured Areas Research Center Program within the framework of the Higher Education Sprout Project by the Ministry of Education in Taiwan.

The authors are with the Department of Electrical Engineering, National Taiwan University of Science and Technology (e-mail: yhliu@mouse.ee.ntust.edu.tw; d10102204@mail.ntust.edu.tw; YF.Luo@mail.ntust.edu.tw).

Digital Object Identifier 10.24295/CPSSTPEA.2018.00018

current and reducing copper and iron loss from the transformer to enhance overall efficiency; however, the auxiliary circuit, winding of the dual transformers, and two rectification output stages complicate the circuit. An auxiliary LC circuit (containing an inductor and a capacitor) was used in [21], which functioned as a variable inductor, providing substantial magnetizing inductance at all times according to the switching frequency to reduce the circulating current of the LLC resonant converter, thereby improving the overall efficiency. Nonetheless, the transformer size becomes larger than that of a conventional LLC resonant converter if the LC auxiliary coil should be winded into the transformer. The research team in [22] modified the design of the transformer and the winding method to improve the overall efficiency of the LLC resonant converter; however, the improvement was limited. In [23], researchers suggested a dynamic adjustment of the dead time (DT) of LLC resonant converters to enhance overall efficiency; this means DT is short when the load is large, and vice versa. This method detected the center point voltage between the high side and low side MOS-FET to determine the optimal timing for ZVS. However, this DT adjustment method is only suitable for region 1 operation of the LLC resonant converter, in which the frequency is higher than the resonant frequency. If employed in other regions of the LLC resonant converter, this method improves efficiency only to a limited extent. When operating in a region with a frequency lower than the resonant frequency, the resonant current value that enables the MOSFET to achieve ZVS is irrelevant to load level but is related to the value of the magnetizing inductance.

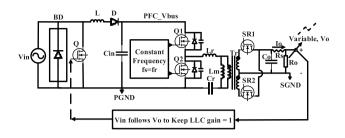

Studies have improved LLC resonant converter efficiency by adjusting LLC input voltage to keep the switching frequency close to the resonant frequency. This methodology comprises three methods: The first method controls LLC resonant converter in an open loop manner [14]-[16]; this method adjusts the input voltage by detecting variations of the output voltage, ensuring that the input-to-output voltage gain of LLC resonant converter stays at 1, as shown in Fig. 2.

The first method is often employed in systems with a variable output voltage, such as battery charging, where an LLC resonant converter only has to provide system isolation and high-efficiency voltage conversion. Additionally, this type of system does not need to consider the transient response.

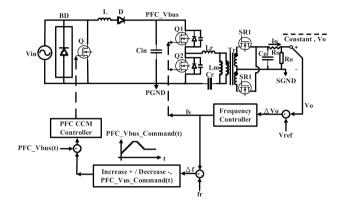

The second method lets the switching frequency track the resonant frequency [3]. When the switching frequency of the LLC resonant converter deviates from the resonant frequency, step-size adjustment is used to adjust the input voltage step by step. This process continues until the switching frequency falls into the setting frequency range, as shown in Fig. 3. However, the step-by-step adjustment of the PFC's input voltage may cause the PFC's output voltage to change frequently, which is unfavorable for regulating voltages at subsequent stages, and the output voltage may oscillate.

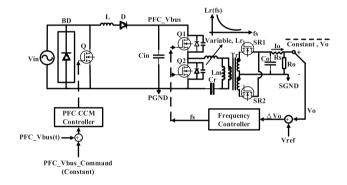

The third method is the use of a variable resonant inductor [13], which engender unsaturated, partially saturated, and saturated resonant inductance values according to various loads and operating points. In addition to the difficulty in controlling the saturation point, this method is unfavorable for realizing com-

Fig. 2. Block diagram of the first method.

Fig. 3. Block diagram of the second method.

Fig. 4. Block diagram of the third method.

mercialization of mass production. The block diagram regarding the function of this architecture is shown in Fig. 4.

This study proposed a novel method for improving efficiency that does not require changes in system architecture and resonant tank components. The proposed method simply utilizes the LLC resonant converter's voltage gain and the switching frequency's open loop relationship under various loads to rapidly estimate the required input voltage compensation, enabling the switching frequency to stay consistent with the resonant frequency. When the load varies, the variable frequency control of the conventional LLC resonant converter changes the switching frequency to alter the voltage gain to compensate for the drop (rise) in the output voltage caused by the increase (decrease) of the load. If the input voltage can be altered while the load changes, voltage gain can thus be changed to achieve optimal operational efficiency under the premise of little variation in the switching frequency. The proposed method is presented in Fig. 5. Because the proposed method does not require a step-by-step

Fig. 5. Block diagram of the proposed method.

Fig. 6 Block diagrams of the PFC stage utilized in this study.

adjustment mechanism, the output response is relatively rapid. Compared with the variable frequency control of a conventional LLC resonant converter, the proposed technology can increase efficiency by 0.8% at full load.

This paper is organized as follows. Section II describes the relationship between the conversion efficiency and the output voltage of PFC. Section III presents the loss analysis of LLC resonant converter operating at the resonant frequency. Section IV derives the proposed control technique. Section V reports the experimental results. Section VI draws some conclusions.

#### II. THE RELATIONSHIP BETWEEN THE EFFICIENCY AND OUTPUT VOLTAGE OF THE PFC STAGE

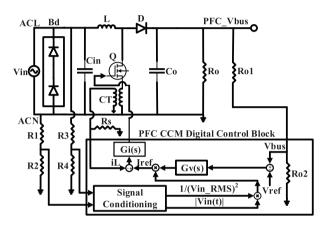

In this paper, an adaptive DC-link voltage control technique is proposed to keep the switching frequency of the LLC resonant converter close to the designed resonant frequency. That is, the output voltage of the PFC stage should be adjustable. In this subsection, the relationship between the conversion efficiency and the output voltage value of the PFC stage is investigated. Fig. 6 shows the block diagram of the PFC stage used in this study.

From Fig. 6, the utilized PFC is a boost converter operated in average current mode [24], [25]. The input voltage range of the utilized 380 W PFC stage is from 90  $V_{AC}$  to 264  $V_{AC}$  with AC line frequency ranges from 47 Hz to 63 Hz, the nominal output voltage is 380 VDC (programmable), and the full load current is 0.92 A. According to [26], the losses of the power MOSFET

TABLE I Key Components of the Utilized PFC Stage

| Key Components            | Manufacturer and Parts     | Specifications                                                                |

|---------------------------|----------------------------|-------------------------------------------------------------------------------|

| Bridge diode (Bd)         | Fairchild, GBU8J           | $V_{\text{RRM}}$ : 600 V, $I_{\text{F(AV)}}$ : 8 A                            |

| MOSFET (Q)                | Infineon, IPP60R199CP      | V <sub>DS</sub> : 650 V, R <sub>DS(on)</sub> :0.199 Ω,<br>I <sub>D</sub> :9 A |

| Freewheeling<br>diode (D) | Cree, C3D10060G            | V <sub>RRM</sub> : 600 V, I <sub>F</sub> :10 A                                |

| Output Capacitor<br>(Co)  | Panasonic,<br>ECOS2WP221CX | 450 V/220 μF                                                                  |

| Controller                | TI, UCD3138                | Integrated Digital Controller                                                 |

Fig. 7. Total losses of the PFC stage utilized in this study.

Q, freewheeling diode D, and output capacitor  $C_o$  relate to the value of the output voltage  $V_o$ . TABLE I shows the key components of the implemented PFC stage. Using the parameters in TABLE I, total losses of the PFC stage can be obtained [26].

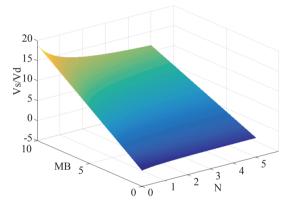

Fig. 7 shows the calculated total losses of the PFC stage under different output voltage  $V_o$  and power level  $P_{in}$ . From Fig. 7, the power losses become larger/smaller when  $V_o$  increases under 300 W/600 W power level. Nonetheless, it can also be observed from Fig. 7 that the variation of power losses for the full voltage swing ( $V_o$  = 320 V to  $V_o$  = 420 V) is rather small (0.045 W (0.015 %) for 300 W level and -0.25 W (0.042 %) for 600 W level). Therefore, changing the output voltage of PFC will have little effect on the overall efficiency.

### III. OPTIMAL OPERATING POINT AND LOSS ANALYSIS OF LLC RESONANT CONVERTER

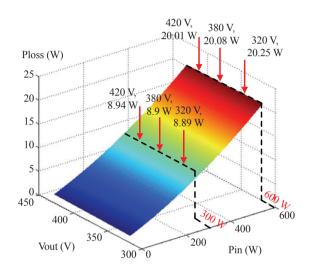

# A. Comparison of Three Operating Points of the LLC Resonant Converter

The key waveforms of the resonant current of LLC converter operating at different switching frequencies are depicted in Fig. 8. If the switching frequency is lower than the resonant frequency as shown in Fig. 8(a), a large circulating current exists in the

Fig. 8. Key waveforms of the resonant current  $i_{Lr}$  of LLC resonant converter operating under different switching frequency.

TABLE II Comparison of the LLC Resonant Converter Operating Under Different Switching Frequency

| LLC Performances                        | fs < fr | fs = fr | $f_S > fr$ |

|-----------------------------------------|---------|---------|------------|

| Turn on loss of primary MOSFET          | ZVS     | ZVS     | ZVS        |

| Turn off loss of primary MOSFET         | Low     | Low     | High       |

| Circulating current in the primary side | High    | Low     | Medium     |

| Secondary diode                         | ZCS     | ZCS     | No         |

| Conduction loss                         | High    | Low     | Medium     |

| Switching loss                          | Low     | Low     | High       |

| Harmonics                               | Low     | Low     | High       |

| Overall performance                     | Medium  | Best    | Medium     |

resonant tank, and it will cause high conduction loss. When the switching frequency equals the resonant frequency, the switching loss and conduction loss are reduced as seen in Fig. 8(b). When the switching frequency is higher than the resonant frequency, the MOSFETs are turned off with higher current as shown in Fig. 8(c); hence, the switching loss increases. TABLE II shows the comparison of the LLC resonant converter operating under different switching frequency [14]. From TABLE II, the LLC resonant converter achieves its best efficiency when operating at the resonant frequency.

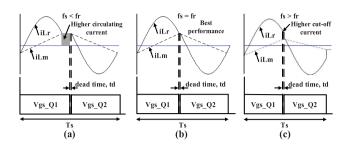

# *B. Loss Analysis for LLC Resonant Converter Operating at the Resonant Frequency*

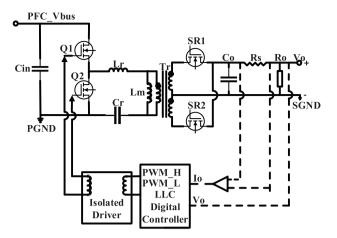

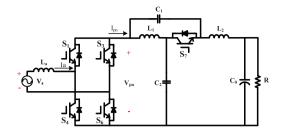

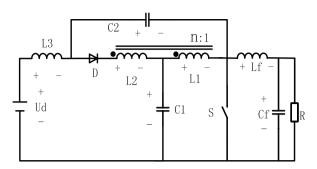

For the proposed control technique, the DC-link voltage will be adjusted to keep the switching frequency of LLC resonant converter near its resonant frequency. Therefore, loss analysis for LLC resonant converter operating at its resonant frequency will be performed first. For the LLC resonant converter utilized in this study, as shown in Fig. 9, the loss model for each component will be briefly derived and described as follows:

#### 1) Losses of MOSFET Q1 and Q2

Conduction loss of MOSFET Q1 and Q2 can be expressed as [15]:

$$P_{LLC-cond} = I_{p-rms}^{2} \cdot R_{DS_on} = \left(\frac{2P_o}{V_o}\sqrt{\frac{R_L^2 T_s^2}{32n^4 L_m^2} + \frac{\pi^2}{8}}\right)^2 \cdot R_{DS_on} \quad (1)$$

where  $I_{p rms}$  is the RMS current of the primary side, transformer

Fig. 9. LLC resonant converter utilized in this study.

turns ratio  $n = N_p/N_s$ ,  $N_p$  is the number of turns on the primary side,  $N_s$  is the number of turns on the secondary side,  $L_m$  is the magnetizing inductance,  $V_o$  is the output voltage,  $R_L$  is the equivalent load resistance and  $T_s$  is the switching period.

Due to its ZVS nature, the turn-on loss of Q1 and Q2 can be neglected. However, there still exists a turn-off loss. The turn-off loss of MOSFETs can be depicted as [14]

$$P_{LLC-sw_off} = 2(\frac{I_{peak}^2 t_f^2 f_s}{48C_{oss}}) = \frac{I_{peak}^2 t_f^2 f_s}{24C_{oss}}$$

(2)

where  $I_{peak}$  is the peak value of the magnetizing current,  $t_f$  is the rise time of the MOSFET,  $f_s$  is the switching frequency, COSS is the output capacitance of MOSFET.

#### 2) Losses of the Isolation Transformer

According to [31], the AC-to-DC resistance ratio  $F_{R_n}$  can be calculated by Dowell's equation, as shown in (3)

$$F_{R_nT_r} = \frac{R_{ac_Tr}}{R_{dc_Tr}}$$

$$= X_n \frac{\sinh 2X_n + \sin 2X_n}{\cosh 2X_n - \cos 2X_n} + 2X_n \frac{m^2 - 1}{3} \frac{\sinh X_n - \sin X_n}{\cosh X_n - \cos X_n}$$

(3)

where  $F_{R_n_T}$  is the AC-to-DC resistance ratio at *nth* harmonic frequency,  $R_{ac_T}$  and  $R_{dc_T}$  are the AC and DC resistance of the transformer, respectively.  $X_n = h/\delta_n$  is the ratio of wire thickness *h* and the skin depth of *nth* harmonic current, *m* is the layer number.

Hence, the AC copper loss of primary and secondary side can be obtained by summing the losses from DC to *nth* harmonics.

$$P_{Copper\_pri} = \sum_{n=0}^{n} F_{R\_n\_pri} R_{dc} \cdot I_{RMS\_pri}^{2}$$

(4)

$$P_{Copper\_sec} = \sum_{n=0}^{n} F_{R\_n\_sec} \cdot R_{dc} \cdot I_{RMS\_sec}^{2}$$

(5)

From (4) and (5), the total copper loss of the transformer can be derived as:

$$P_{Copper\_T_r} = P_{Copper\_pri} + P_{Copper\_sec}$$

(6)

The core loss of the transformer can be calculated using the empirical Steinmetz equation [27], [28], as shown in (7):

$$P_{Core} = K_{core} \cdot f^{\alpha} \cdot \Delta B_{Tr}^{\beta} \cdot V_e \tag{7}$$

where  $K_{core}$  is the Steinmetz coefficient of the core,  $V_e$  is the volume of the core and  $\Delta B_{Tr}$  is the flux swing of the transformer and can be calculated as:

$$\Delta B_{Tr} = \frac{V_{LM} \cdot D \cdot T_s}{N_p \cdot A_e} = \frac{nV_o \cdot T_s}{4 \cdot N_p \cdot A_e}$$

(8)

where  $V_{LM}$  is the voltage of magnetizing inductance, D is the duty ratio,  $T_s$  is the switching period,  $A_e$  is the effective cross-sectional area of the core.

#### 3) Losses of the Resonant Inductor

The losses in the resonant inductor include copper loss and core loss, and can be obtained as [14], [31]:

$$P_{Copper\_Lr} = \sum_{n=0}^{n} F_{R\_n\_Lr} \cdot R_{dc\_Lr} \cdot I_{Lr}^{2}$$

(9)

where the AC-to-DC resistance ratio  $F_{R_nL} = R_{ac_Lr}/R_{dc_Lr}$ ,  $R_{ac_Lr}$  and  $R_{dc_Lr}$  are the AC and DC resistance of the resonant inductor, respectively.  $I_{Lr}$  is the RMS value of the resonant inductor current.

Similarly, the core loss of the resonant inductor can be obtained using the empirical Steinmetz equation [14], [27], [28], as depicted in (10)

$$P_{Core\_Lr} = K_{core\_Lr} \cdot f^{\alpha} \cdot \Delta B_{Lr}^{\ \beta} \cdot V_{e\_Lr}$$

(10)

where  $K_{core\_Lr}$  is the Steinmetz coefficient of the resonant inductor,  $V_{e\_Lr}$  is volumn of the resonant inductor, and  $\Delta B_{Lr}$  is the flux swing of the resonant inductor, as shown in (11)

$$\Delta B_{Lr} = \frac{L_r}{n_{Lr} A_{e_{-Lr}}} \sqrt{\left(\frac{nV_o T}{4L_m}\right)^2 + \left(\frac{\pi V_o I_o}{2V_{dc}}\right)^2}$$

(11)

where  $n_{Lr}$  is the number of turns on the resonant inductor,  $A_{e_{L}r}$  is the effective cross-sectional area of the resonant inductor and  $V_{dc}$  is the input voltage of the LLC converter.

#### 4) Losses of the Synchronous Rectifier (SR) S1 and S2

The conduction loss of synchronous rectifier can be calculated as:

$$P_{LLC\_SR\_cond} = I_{s\_rms}^{2} \cdot R_{DS\_on}$$

(12)

where  $I_{s rms}$  can be expressed as [35]

$$I_{s_{-}rms} = \frac{\sqrt{3}}{24\pi} \frac{V_o}{R_L} \sqrt{\frac{(5\pi^2 - 48)n^4 R_L^2 T_s^2}{L_m^2} + 12\pi^2} \quad (13)$$

When operating at its resonant frequency, the SR of LLC resonant converter exhibits ZCS; hence, the switching loss of SR is neglected.

#### 5) Total Losses of the LLC Resonant Converter

Based on the above derivation, the total losses of the LLC resonant converter can be obtained by summing up the losses of each component shown in Fig. 9.

#### IV. OPERATING PRINCIPLE OF THE PROPOSED METHOD

In this paper, a novel adaptive DC-link control technique is proposed. With this approach, the LLC resonant converter will automatically adjust its input voltage to keep the switching frequency of the LLC resonant converter close to the resonant frequency so that the conversion efficiency of the LLC resonant converter can be optimized across the whole load range. According to the First Harmonic Approximation (FHA) technique, the voltage gain of the LLC resonant converter can be expressed as:

$$M(f_{n}) = \frac{V_{o}}{V_{in}/(2 \cdot n)}$$

$$= \left| \frac{L_{n} \cdot f_{n}^{2}}{[(L_{n}+1) \cdot f_{n}^{2} - 1] + j[(f_{n}^{2}-1) \cdot f_{n} \cdot Q_{e} \cdot L_{n}]} \right|$$

(14)

where  $L_n = L_m/L_r$  is the ratio of the magnetizing inductance and resonant inductance,  $f_n = f_s/f_r$  is the ratio of switching frequency and resonant frequency. In (14), the quality factor Q<sub>e</sub> can be depicted as

$$Q_e = \frac{\sqrt{L_r/C_r}}{R_e} \tag{15}$$

where the equivalent load resistance  $R_e$  can be obtained as

$$R_e = \frac{8 \cdot n^2}{\pi^2} R_o = \frac{8 \cdot n^2}{\pi^2} \frac{V_o}{I_o}$$

(16)

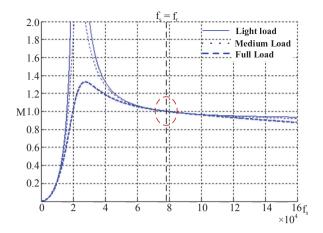

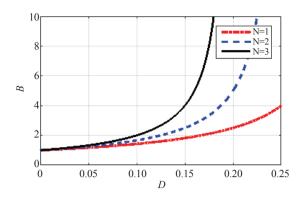

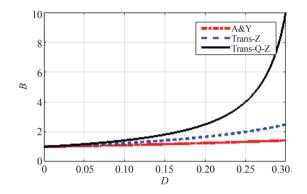

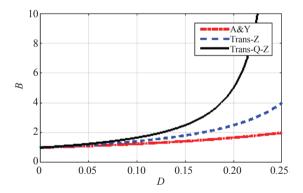

Fig. 10 shows the voltage gain curves of different values of load current. From Fig. 10, the voltage gain is irrelevant to the load current if the switching frequency is fixed at the resonant frequency. However, if non-idealities such as losses in power switches, magnetics, and diodes are taken into account, the actual output voltage will vary according to the load current [36]. When load increases/decreases, the output voltage will drop/ rise accordingly. Hence, a closed-loop controller is typically required to adjust the switching frequency to compensate the voltage variation. That is, to compensate for the effect of the varied load value, a conventional LLC resonant converter operates under a wide switching frequency variation range. However, wide frequency variation complicates the design of the LLC resonant converter and leads to a decrease of efficiency.

To deal with this problem, an adaptive DC-link voltage control method is proposed in this study. From (14), the output voltage under ideal condition can be expressed by:

Fig. 10. Gain curves of the LLC resonant converter under different load conditions (ideal case).

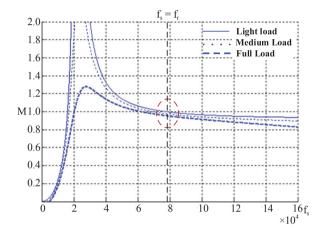

Fig. 11. Gain curves of the LLC resonant converter under different load conditions (non-ideal case).

$$V_{o} = \frac{V_{in}}{2 \cdot n} \cdot M = \frac{V_{in}}{2 \cdot n} \cdot \left| \frac{L_{n} \cdot f_{n}^{2}}{[(L_{n} + 1) \cdot f_{n}^{2} - 1] + j[(f_{n}^{2} - 1) \cdot f_{n} \cdot Q_{e} \cdot L_{n}]} \right|$$

$$= \frac{V_{in}}{2 \cdot n} \cdot M(f_{n}, Q_{e})$$

(17)

Taking all the non-idealities into consideration, the actual output voltage can be modified as:

$$V_o = \frac{V_{in}}{2 \cdot n} \cdot M(f_n, Q_e) - I_o \cdot R_T$$

(18)

where  $R_T$  is the equivalent resistance represents the cumulative effect of all losses and can be obtained through experiments.

Fig. 11 shows the gain curve of the utilized LLC resonant converter under different load conditions when taking all the non-idealities into account. From Fig. 11, the gain value varies even when the operating frequency is fixed at the resonant frequency. Therefore, some control technique should be employed to compensate for this gain variation.

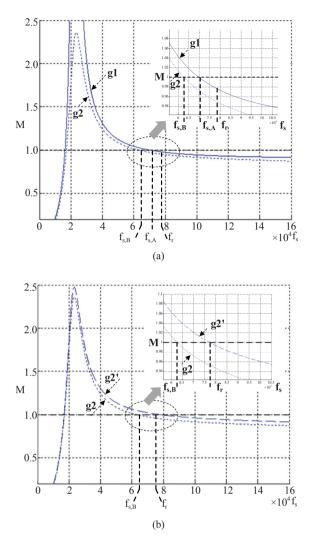

Fig. 12 shows the changes of the gain curves of the LLC resonant converter to explain the concept of the proposed control.

Fig. 12. Changes of gain curve under load variation in conventional and proposed control methods.

In conventional frequency control, when the load current varies from light load to heavy load condition, the gain curve changes from g1 (solid line) to g2 (dotted line). To maintain the output voltage, the controller adjusts the switching frequency of the main switches Q1 and Q2 from  $f_{s,A}$  to  $f_{s,B}$  to regulate the output voltage, as shown in Fig. 12 (a). On the other hand, when the load current changes from light load to heavy load in the proposed control, the output voltage is regulated by adjusting the input voltage (which consequently changes the gain curve) instead of the switching frequency as shown in Fig. 12 (b). That is, the gain curve changes from g2 (dotted line) to g2' (dashed line) to achieve a constant gain at the resonant frequency  $f_r$ .

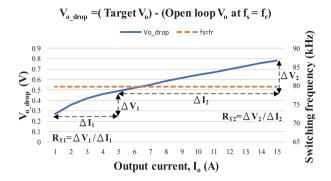

The derivation of the proposed control mechanism can be explained as follows. According to (18), the output voltage variation  $V_{o, drop}$  equals to the voltage drop across  $R_T$ , that is,  $V_{o, drop} = I_o * R_T$ . To compensate for this voltage drop, the required voltage variation of input voltage  $\Delta V_{in}$  can be calculated as

$$\Delta V_{in} = \frac{2 \cdot n \cdot V_{o,drop}}{M(f_n, Q_e)} = \frac{2 \cdot n \cdot I_o \cdot R_T}{M(f_n, Q_e)}$$

(19)

Fig. 13. Flowchart of the proposed method.

Since the gain value of the LLC resonant converter is always close to 1.0 when operating at the resonant frequency, (19) can be approximated as

$$\Delta V_{in} = 2 \cdot n \cdot I_o \cdot R_T \tag{20}$$

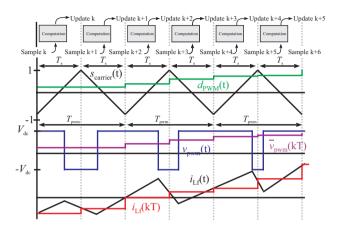

Fig. 13 shows the flowchart of the proposed method. At first, the controller will determine whether the load detection time has been reached. In this study, the load detection time is 0.3 second. If yes, the load current value  $I_a$  will be measured and the controller will check if the load change has occurred or not. Otherwise, only original closed-loop control will be performed. If the load level changes, the required compensation voltage can be obtained using (20). In (20), the equivalent resistance  $R_T$ which represents the cumulative effect of all losses can be obtained by operating the LLC resonant converter at the resonant frequency using open loop control and recording voltage drop value under various load conditions. By adjusting the input voltage value and hence changing the gain curve shape, switching frequency of the resonant LLC converter can be kept around its resonant frequency. Since the adaptive DC-link voltage control scheme leads to reduced frequency variation range, optimal design of the LLC resonant converter and high efficiency under all-load conditions can be guaranteed. It should be noted that the load detection time should be slower than the bandwidth of the voltage control loop of PFC stage; otherwise the proposed method may fail to perform correctly.

The block diagram of the realized two-stage SPS with adaptive DC-link voltage control is illustrated in Fig. 14. From Fig. 14, the only measured signals are the output voltage  $V_o$  and output current  $I_o$ . After calculating the required input voltage variation  $\Delta V_{in}$ , this command will be sent to PFC front stage via universal asynchronous receiver transmitter (UART) and the PFC stage will adjust its output voltage as proposed in [3], the input voltage only changes once for the proposed method each

Fig. 14. Block diagram of the proposed method.

TABLE III Components Utilized in the Implemented LLC Resonant Converter

| Key Components        | Manufacturer and Parts    | Specifications                                                                      |  |  |

|-----------------------|---------------------------|-------------------------------------------------------------------------------------|--|--|

| MOSFET (Q)            | Infineon,<br>SPW20N60CFD  | V <sub>DS</sub> : 650 V,<br>R <sub>DS(on)</sub> : 0.22 Ω,<br>I <sub>D</sub> : 20.7A |  |  |

| Synchronous Rectifier | Infineon,<br>IRLB3036GPbF | V <sub>DS</sub> : 60 V,<br>R <sub>DS(on)</sub> : 1.9 mΩ,<br>I <sub>D</sub> : 195 A  |  |  |

| Transformer           | Np:48, Ns:3, Ns:3         | L <sub>m</sub> : 520 μH                                                             |  |  |

| Output Capacitor (Co) | Nichicon,<br>PLF1C471MD01 | 16 V/470 µF * 5                                                                     |  |  |

| Controller            | TI, UCD3138               | Integrated Digital<br>Controller                                                    |  |  |

time the load changes. Hence, the transient response can be improved and the output voltage oscillation phenomenon can be avoided.

#### V. EXPERIMENTAL RESULTS

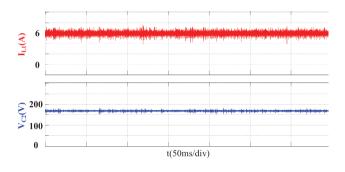

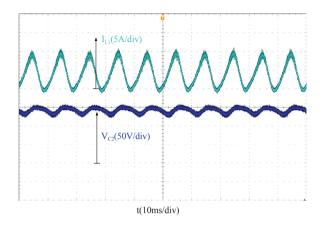

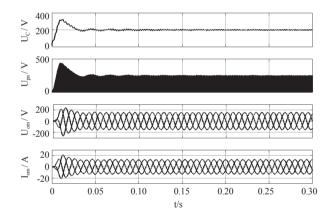

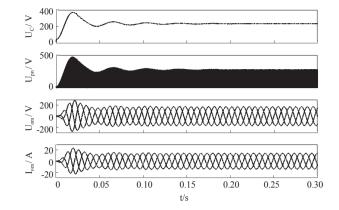

In order to validate the correctness and effectiveness of the proposed method, a 350 W prototyping circuit is first constructed. The input voltage range of the implemented LLC resonant converter is from 350 V<sub>DC</sub> to 420 V<sub>DC</sub>, the output voltage is fixed at 12 V<sub>DC</sub> and the full load current is 29 A. Table III shows the specific components utilized in the implemented prototyping circuit and their corresponding values.

Fig. 15 displays the procedure for obtaining the equivalent resistance  $R_T$ . In Fig. 15, the realized LLC resonant converter operates at the resonant frequency using open loop control, and the load current changes from 1 A to full-load 29 A with an interval of 1 A. After measuring the voltage variation  $V_{o,drop}$ ,  $R_T$  can be approximated by calculating the slope of the  $V_{o,drop}$  versus  $I_o$  curve. In this study,  $R_T = 37.9 \text{ m}\Omega$  when load current is lower than 5 A and  $R_T = 15.0 \text{ m}\Omega$  when load current is higher than 5 A, as shown in Fig. 15.

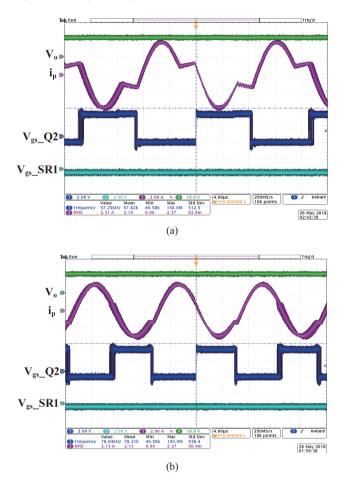

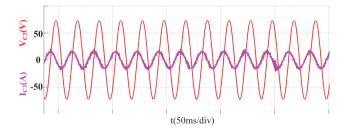

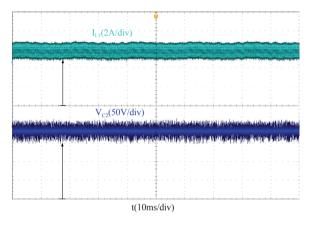

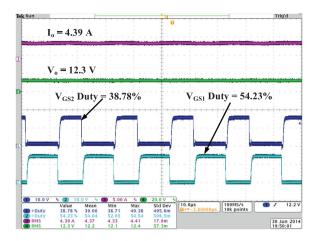

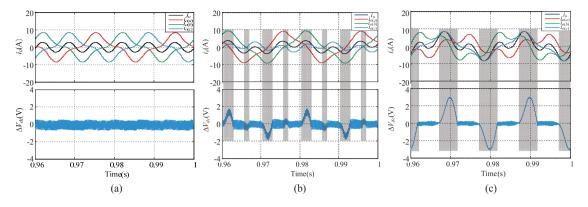

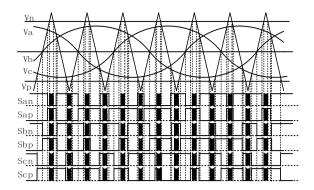

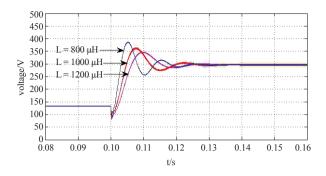

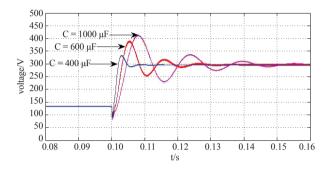

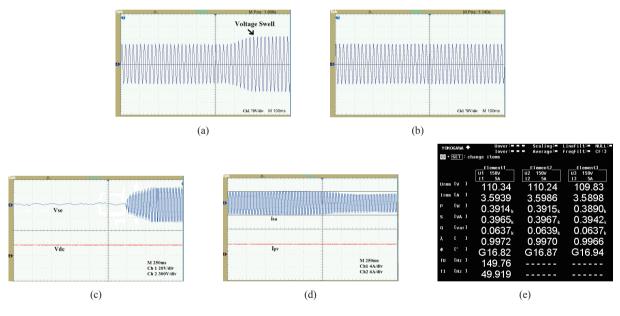

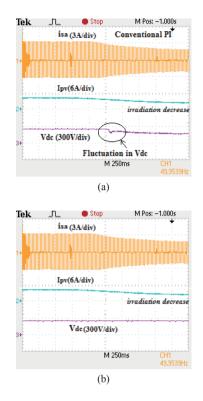

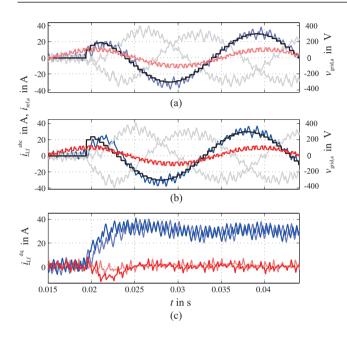

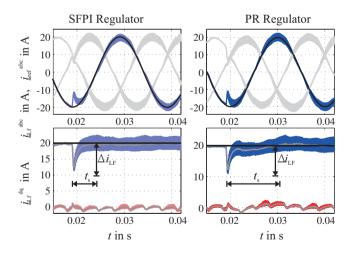

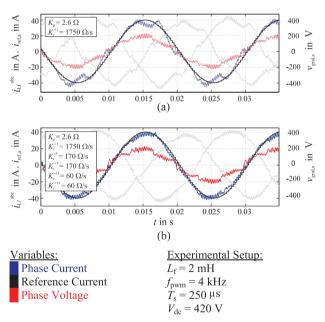

Fig. 16(a) and (b) shows the key waveforms of the conventional and proposed converters in full load condition, respectively. From Fig. 16, the operating frequency of the conventional LLC resonant converter is 57.25 kHz and the operating frequency of the proposed method is 78.64 kHz, which reduces

Fig. 15. Obtaining R<sub>T</sub> via experiments.

Fig. 16. Key waveforms at full load. (a) Conventional control (b) Proposed control.

the circulating loss and the switch turn-off loss in the primary side. Moreover, the proposed converter achieves ZVS over the entire load conditions. In Fig. 16(b), the input voltage changes from 380 V to 407 V to maintain the switching frequency near the resonant frequency.

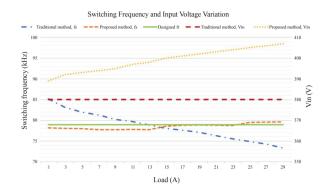

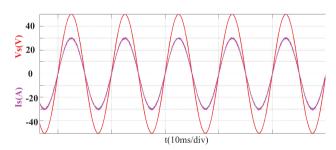

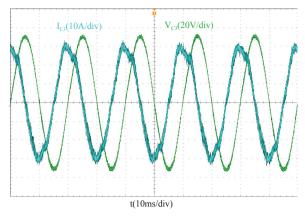

Fig. 17 shows the operating frequency range and the input voltage variation of the LLC resonant converter for both the conventional and the proposed method. As shown in Fig. 17, the frequency range of the convention technique is from 85 kHz to 73 kHz. In contrast, the frequency variation is from 76 kHz to

Fig. 17. Comparison of the operating frequency range and input voltage variation.

Fig. 18. Measured efficiency curves of the proposed adaptive DC-link voltage control method.

80 kHz for the proposed control method. It can also be observed from Fig. 17 that the input voltage of the conventional LLC resonant converter is fixed at 380 V while the input voltage of the proposed scheme changes from 389 V at light load to 407 V at full load. From Fig. 17, the DC-link voltage can be effectively adjusted to keep the switching frequency of LLC resonant converter near its resonant frequency.

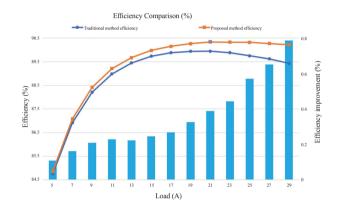

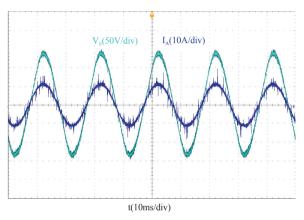

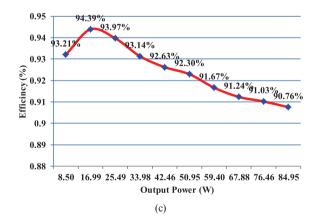

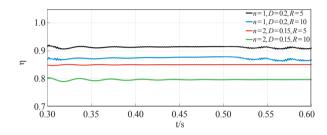

Fig. 18 shows the measured efficiency curves of the proposed adaptive DC-link voltage control method and the conventional variable frequency control technique as load changes from 5 A to 29 A. From Fig 18, the proposed control technique achieves higher efficiency under all load conditions as compared to conventional LLC resonant converter, the efficiency improvement percentages are 0.13%, 0.27% and 0.88% under light-load, half-load and full-load conditions, and the averaged efficiency improvement is 0.427%. In addition, the highest measured efficiency is 90.22%.

#### VI. CONCLUSION

In this study, an adaptive DC-link voltage control technique for a two-stage SPS with LLC resonant converter is proposed. With this presented technique, the DC-link voltage increases to compensate for the voltage drop caused by load variation, which facilitates the resonant LLC converter to operate near its resonant frequency. This decreases the circulating energy and makes the optimal design of an LLC resonant converter possible. Consequently, efficiency improvement can be achieved without any additional auxiliary circuits. According to the experimental results, the switching-frequency-variation range is reduced from 12 kHz to 4 kHz and the efficiency of the proposed method can be improved up to 0.13%, 0.27% and 0.88% under light-load, half-load, and full-load conditions, respectively.

#### References

- M. Kasper, D. Bortis, G. Deboy, and J.W. Kolar, "Design of a highly efficient (97.7%) and very compact (2.2 kW/dm3) isolated AC-DC telecom power supply module based on the multicell ISOP converter approach," *IEEE Transactions on Power Electronics*, vol. 32, no. 10, pp. 7750-7769, Oct. 2017.

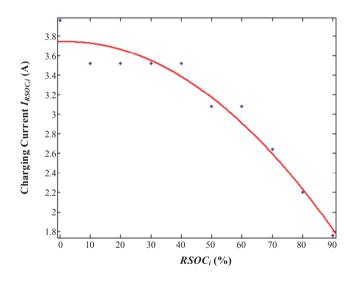

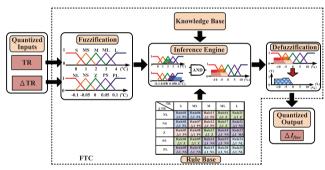

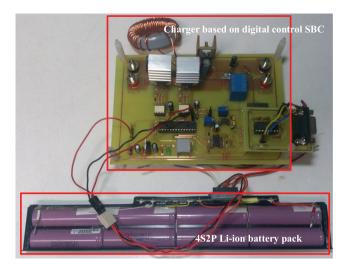

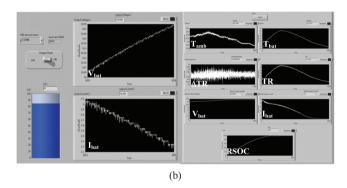

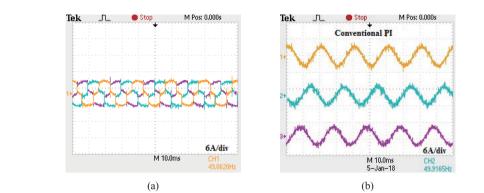

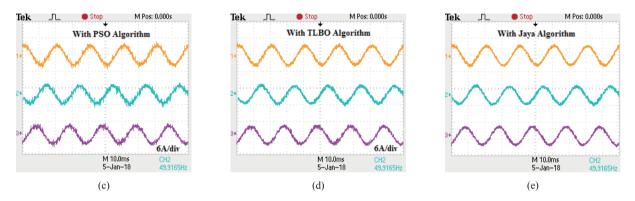

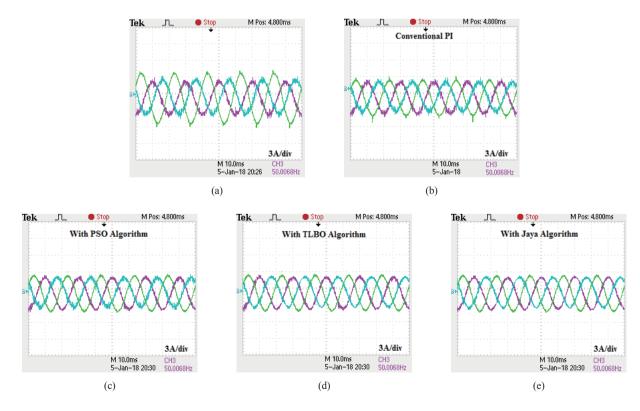

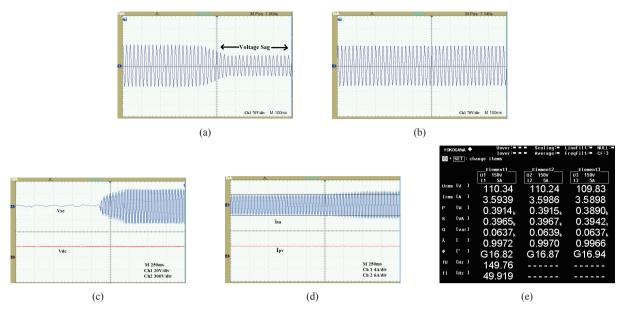

- [2] Y. S. Lai and Z. J. Su, "New integrated control technique for twostage server power to improve efficiency under the light-load condition," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 11, pp. 6944-6954, Nov. 2015.