37

## CPSS Transactions on **Power Electronics and Applications** VOLUME 2 NUMBER 2 JUNE 2017

#### INAUGURAL SPECIAL ISSUE ON THE DEVELOPING TRENDS OF POWER ELECTRONICS: PART 3

#### EDITORIAL

| Editorial for the Inaugural Special Issue on the Developing Trends of Power Electronics: Part 3 |  |

|-------------------------------------------------------------------------------------------------|--|

| J. Liu                                                                                          |  |

#### SPECIAL ISSUE INVITED PAPERS

| Perspective of Loss Mechanisms for Silicon and Wide Band-Gap Power Devices                      |     |

|-------------------------------------------------------------------------------------------------|-----|

| G. Deboy, O. Haeberlen, and M. Treu                                                             | 89  |

| Review of Power Semiconductor Device Reliability for Power Converters                           |     |

| B. Wang, J. Cai, X. Du, and L. Zhou                                                             | 101 |

| 15 kV SiC MOSFET: An Enabling Technology for Medium Voltage Solid State Transformers            |     |

|                                                                                                 | 118 |

| Opening the Box: Survey of High Power Density Inverter Techniques From the Little Box Challenge |     |

| K. A. Kim, YC. Liu, MC. Chen, and HJ. Chiu                                                      | 131 |

#### **REGULAR PAPERS**

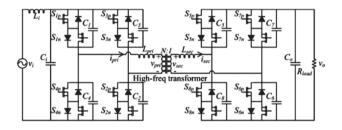

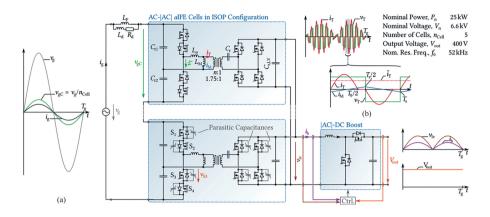

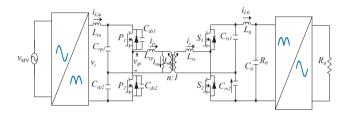

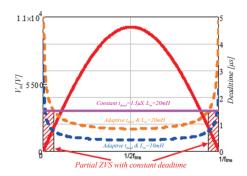

| Analysis and Cell-Level Experimental Verification of a 25 kW All-SiC Isolated Front End 6.6 kV/400 V |     |

|------------------------------------------------------------------------------------------------------|-----|

| AC-DC Solid-State TransformerJ. E. Huber, J. Böhler, D. Rothmund, and J. W. Kolar                    | 140 |

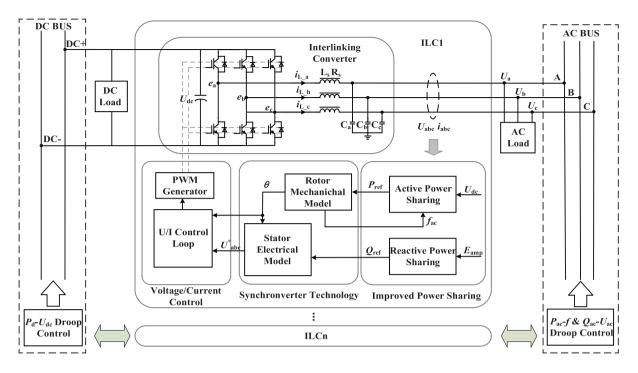

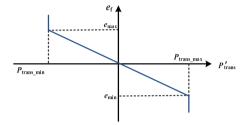

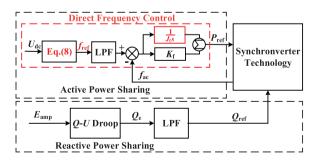

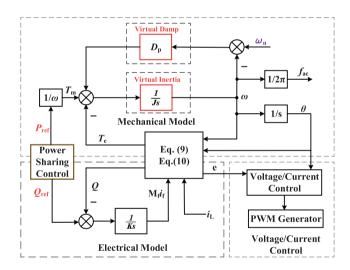

| Improved Control Strategy of Interlinking Converters With Synchronous Generator Characteristic in    |     |

| Islanded Hybrid AC/DC MicrogridG. Qi, A. Chen, and J. Chen                                           | 149 |

#### **CPSS TRANSACTIONS ON POWER ELECTRONICS AND APPLICATIONS**

CPSS Transactions on Power Electronics and Applications (CPSS TPEA) is sponsored and published by China Power Supply Society and technically co-sponsored by IEEE Power Electronics Society. It publishes original and high quality peer reviewed papers in the field of power electronics and its applications. With the goal of promoting the technology of power electronics including concepts, theory, modeling and control, analysis and simulation, emerging technology and applications, CPSS TPEA is expected to be a favorable platform to strengthen information exchange in this area. Interested authors are welcome to submit your papers via the Manuscript Central (https://mc03.manuscriptcentral.com/tpea-cpss) online submission system. You can find more information on our website: http://tpea.cpss.org.cn.

#### **CPSS and PELS Joint Advisory Committee**

**Prof. Dehong Xu** Zhejiang University, China President of CPSS

**Prof. Jiaxin Han** The Institute of Seawater Desalination and Multipurpose Utilization, China Secretary General of CPSS

**Prof. Jinjun Liu** Xi'an Jiaotong University, China Vice President of CPSS and Executive Vice President of PELS

#### **Editor-in-Chief**

JINJUN LIU Xi'an Jiaotong University, China E-mail: jjliu@xjtu.edu.cn

#### **Editorial Office**

Tel: +86-22-27680796-18# Fax: +86-22-27687886 E-mail: tpea@cpss.org.cn Website: tpea.cpss.org.cn **Prof. Braham Ferreira** Delft University of Technology, Netherlands President of PELS

**Dr. Don Tan** Northrop Grumman Corporation, USA Past President of PELS

**Prof. Frede Blaabjerg** Aalborg University, Denmark Vice President of PELS

# Editorial for the Inaugural Special Issue on the Developing Trends of Power Electronics: Part 3

WITH this editorial, we sincerely welcome our readers to the brand-new publication — CPSS Transactions on Power Electronics and Applications (CPSS TPEA). It is sponsored and published by China Power Supply Society (CPSS) and technically co-sponsored by IEEE Power Electronics Society (IEEE PELS).

CPSS was founded in 1983 and has been the only top-level national academic society in China that solely focuses on the power supply/power electronics area. In the past 30plus years CPSS has dedicated to provide to its members, researchers, and industry engineers nationwide with high quality services including conferences, technical training, and various publications, and this in deed has helped the society build up its membership rapidly, which now totals up to more than 4000 individual members plus 500 enterprise members. The fast growth of membership in turn compels CPSS to always work out better services for its members, one of which being the open-up of this periodical — a new journal in English language as a publication platform for international academic exchanging. This of course needs to be done through international cooperation, and that's why IEEE PELS is tightly involved, being the premier international academic organization in power electronics area and one of the fastest growing technical societies of the Institute of Electrical and Electronics Engineers (IEEE).

To fulfill the publishing need of the fast-developing power electronics technology worldwide is a more important purpose of launching this new journal. So far there are only 3 or 4 existing journals which are concentrated on power electronics field and have global reputation. For quite a few years people in the international power electronics community have had the feeling that, the existing journals have not even come close to meeting the huge demand of global academic and technology exchanges. E.g., the two existing IEEE power electronics journals, i.e. IEEE Transactions on Power Electronics (IEEE TPEL) and IEEE Journal of Emerging and Selected Topics in Power Electronics (IEEE JESTPE), now publish about 1000 papers a year, which is under a very low paper acceptance rate of around 25%, but still have a back-log of about one year for the newly accepted papers to finally appear in printed form to the public. The addition of this new dedicated journal would be an ideal improvement to fulfill such a tremendous need.

The booming of publishing need really is an indicator of how fast power electronics has been developing in recent years. Innovations have been continuously coming up from component (both active device and passive device), module, circuit, converter, to system level, covering different technical aspects as topology or structure conceiving, modeling and analysis, control and design, and measurement and testing. New issues and corresponding solutions have been continuously presenting as the applications of power electronics prevail horizontally in almost every area and corner of human society, from industry, residence and commerce, to transportations, and penetrate vertically through every stage of electric energy flow from generation, transmission and distribution, to utilization, in either a public power grid or a stand-alone power system. I personally believe that we are entering a world with "more electronic" power systems. The prediction around 30 years ago, that power electronics one day will become one of the major poles supporting the human society, is coming into reality. And I also believe, that power electronics is going to last for long time as an important topic since it is one of the keys to answer a basic question for human society, which is how human can harness energy more effectively and in a manner friendlier to both the user and the environment.

Therefore, I assume that there is probably no better fitting as for CPSS TPEA to publish its first few issues under a special topic about the developing trends of power electronics. We have invited a group of leading experts in different areas of power electronics to write survey/review papers or special papers with review/overview nature to some extent. To publish in a timely and regular style, we organize this inaugural Special Issue into different parts. Part 1 and 2 were published in the December issue last year and the March issue this year respectively, Part 3 appears in this June issue, and the following part is scheduled for the September issue.

In Part 3 we are honored to have 4 invited papers. For the first two, each addresses one hot topic in the area of power semiconductor devices: power loss mechanism and reliability. The next two follow up with the state-of-the-arts in the applications of new power semiconductor devices, one application being solid state transformers and the other being single-phase inverters.

We begin with a paper on the power loss mechanisms for silicon and wide band-gap power semiconductor devices. It is co-authored by Dr. Gerald Deboy and his team from Infineon Technologies. It presents a detailed comparison between the latest generation Super Junction power transistors and e-mode GaN HEMTs and SiC MOSFETs in terms of semiconductor power losses and their potential for further improvement, with a short application section showing the best matching circuits for each device.

The second paper provides a review on the reliability of power semiconductor devices used in power converters.

It is written by Prof. Luowei Zhou and his research group from Chongqing University, and presents a broad overview of reliability researches for power semiconductor devices, including failure mechanisms, condition monitoring, lifetime evaluation and active thermal control. The current issues and future challenges on the reliability of power semiconductor devices are also provided.

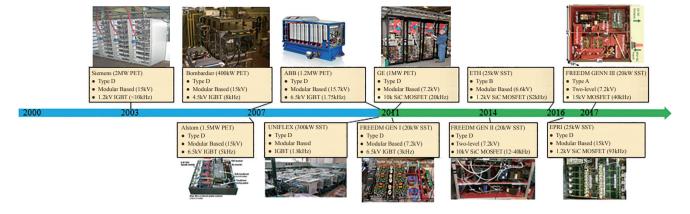

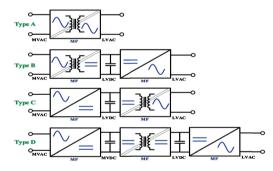

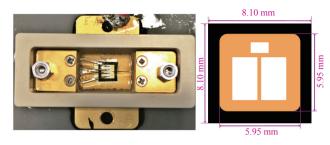

The third paper is about the application of a new power semiconductor device in medium voltage (MV) solid state transformers. It is written by Dr. Alex Q. Huang and his research group from North Carolina State University. It reviews the characteristics of 15 kV SiC MOSFET and offers a comprehensive guideline of implementing this device in solid state transformers and other possible MV power conversion scenarios in terms of topology selection, loss optimization and thermal management.

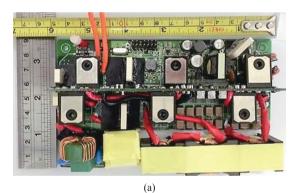

Last but not least, the fourth paper is written by Dr. Huang-Jen Chiu and his research group from National Taiwan University of Science and Technology in cooperation with Dr. Katherine A. Kim from Ulsan National Institute of Science and Technology. The paper focuses on the Little Box Challenge (LBC) — a competition sponsored by Google and the IEEE Power Electronics Society in 2014-2015, where participants were challenged to design a high power-density single-phase 2-kVA inverter. The paper surveys the designs from eight different participating teams, shares experimental results from the Taiwan Tech team, and highlights some interesting innovations from the teams that participated in the LBC.

I'd like to thank the authors of all these 4 invited papers. It's their high-quality contributions that finally leads to the launching of this new journal. I'd like to thank Dehong Xu, President of CPSS, who in 2015 initiated the idea of publishing the new journal and since then has been persistently supporting my work as the founding Editor-in-Chief. I'd also like to thank Jiaxin Han, Secretary General of CPSS, Jan A. Ferreira, President of IEEE PELS, 2015-2016, Don F. D. Tan, President of IEEE PELS, 2013-2014, and Frede Blaabjerg, IEEE PELS Vice President for Products, 2015-2018, who form the CPSS and IEEE PELS Joint Advisory Committee for our new journal with Dehong Xu and myself. Other IEEE officers and leading staffs like Dushan Borojevich, PELS President, 2011-2012, Alan Mantooth, PELS President, 2017-2018, Mike Kelly, PELS Executive Director, and Frank Zhao, Director of China Operations, IEEE Beijing Office, just to name a few, also provided continuous support and constructive advices. My earnest thanks also go to the CPSS Editorial Office led by Lei Zhang, Deputy Secretary General of CPSS, for their wonderful editing work. It would not have been possible to create a new journal in such a short time without their efforts. I'd like to finally thank all the members of the Executive Council of CPSS and particularly the leaders of Chinese power electronics industry. They always firmly stand behind CPSS TPEA and ready to help whenever needed.

> JINJUN LIU, *Editor-in-Chief*, Xi'an Jiaotong University, 28 West Xianning Road, Xi'an, Shaanxi 710049 CHINA E-mail: jjliu@mail.xjtu.edu.cn

Jinjun LIU received his B.S. and Ph.D. degrees in Electrical Engineering from Xi'an Jiaotong University (XJTU), China in 1992 and 1997 respectively. He currently holds the position of XJTU Distinguished Professor of Power Electronics, sponsored by Chang Jiang Scholars Program of Chinese Ministry of Education.

Dr. LIU coauthored 3 books (including a textbook), published over 200 technical papers in peer-reviewed journals and conference proceedings, and holds more than 30 invention patents (China/USA).He received for 7 times governmental awards at national level or provincial/ministerial level for scientific research achievements or academic/teaching career achievements.He also received the 2006 Delta Scholar Award, the 2014 Chang Jiang Scholar Award, the 2014 Outstanding Sci-Tech Worker of the Nation Award, and the IEEE Transactions on Power Electronics 2016 Prize Paper Award.His research interests are power quality control and utility applications of power electronics, micro-grids for sustainable energy and distributed generation, and more/all electronic power systems.

Dr. Liu has served as the IEEE Power Electronics Society (PELS) Region 10 Liaison and then China Liaison for 9 years, an Associate Editor for the IEEE Transactions on Power Electronics for 9 years, and starting from 2015 the Vice President for membership of IEEE PELS. He is on Board of China Electrotechnical Society (CES) and was elected to a Vice President of the CES Power Electronics Society in 2013. He is the Vice President for International Affairs, China Power Supply Society (CPSS) and the inaugural Editor-in-Chief of CPSS Transactions on Power Electronics and Applications.

## Perspective of Loss Mechanisms for Silicon and Wide Band-Gap Power Devices

Gerald Deboy, Oliver Haeberlen, and Michael Treu

Abstract—With the commercial availability of GaN and SiCbased power semiconductor devices having significantly improved material characteristics, there is a need to discuss the perspective of the underlying physical loss mechanisms of these devices versus their silicon counterparts. This article will compare latest generation Superjunction power transistors versus e-mode GaN HEMTs and SiC MOSFETs in terms of semiconductor losses and their potential for further improvement. A short application section will give practical information on best matching circuits for each device concept.

*Index Terms*—GaN HEMT, loss mechanisms, power semiconductor devices, Superjunction, wide bandgap devices.

#### I. INTRODUCTION

THROUGH the introduction of the Superjunction principle [1]-[3], the characteristics of silicon based power MOSFETs could be greatly improved extending the life cycle of this technology up to now and potentially far into the future. Continuous improvement of the technology and major cost-down steps in the fabrication have made Superjunction transistors the first choice for high voltage power devices in the 500 V to 800 V domain. AC to DC power converters in a wide variety of applications such as lighting, adapter, server and telecom power supplies, and EV charging are based on Superjunction transistors as the prevailing technology utilizing a number of well-established power circuits and control methods.

With the arrival of GaN High Electron Mobility Transistors (HEMT) as a potentially game-changing technology [4] new topologies and control methods are challenging classic power supply architectures.

As it is rarely meaningful to put entirely new devices into existing sockets, it is worthwhile to analyze the underlying physical loss mechanisms both for wide band-gap devices and Superjunction transistors. Based on this loss analysis best matches in terms of circuits and control methods are identified. Starting from today's achievements we will give an outlook into further improvement potential with respect to semiconductor losses.

Section II will introduce the limit line of silicon and ways to overcome it with various device concepts. Perspectives are given to further lower the on-state resistance. In Section III, switching losses are derived from a physical understanding of the mechanisms inside the device. The influence of control and application circuit is discussed. Experimentally measured values are given both for e-mode GaN HEMTs and latest generation of Superjunction devices.

Based on the loss analysis Section IV suggests best matching circuits and control methods for each power device concept.

A short summary will conclude the article.

#### II. DEVICE CONCEPTS AND THEIR POTENTIAL TOWARDS LOWERING THE ON-STATE RESISTANCE

#### A. The Limit Line of Silicon

The optimization of the specific on-state resistance has always been a strong driving factor for the semiconductor industry as it allows differentiation from competition through lower  $R_{DS(on)}$  in a given package as well as to lower costs through fabricating more dies on the same wafer.

In the simplest case, the dependency of the on-state resistance can be derived from the Poisson equation in a one-dimensional way as:

$$R_{on} = \frac{4BV^2}{\mu\varepsilon E_c^3}.$$

(1)

Modeling silicon's dependency of the critical electric field on doping concentration in an empirical way leads to the well-known formula:

$$R_{on} \approx 8.3 \times 10^{-9} BV^{2.5} \Omega \cdot cm^2$$

. (2)

This relation is known as the "silicon limit". It describes the best specific on-state resistance, which can theoretically be achieved for a given breakdown voltage in case of a one-dimensional p-n junction. It is noteworthy that the optimum doping profile is not constant as function of depth, but shows an increase towards the drain electrode [5] following a hyperbolic sine function. Practically, margins need to be considered both for voltage and  $R_{DS(on)}$ . Commercial products are therefore typically 20% or more above the limit line [6].

Improvements beyond this barrier have been the subject for research for many decades. In principle there are three fundamental concepts:

1) Changing the material system towards wide band-gap. SiC MOSFETs and JFETs follow this path.

Manuscript received June 19, 2017.

The authors are with the Infineon Technologies Austria AG, Siemensstraße 2, 9500 Villach, Austria (e-mail: Gerald.Deboy@infineon.com; Oliver.

Haeberlen@infineon.com; Michael.Treu@infineon.com).

Digital Object Identifier 10.24295/CPSSTPEA.2017.00010

- Breaking away from the limitations of the one-dimensional Poisson equation by introducing two- or three-dimensional structures. Superjunction devices and field plate (or shielded gate) concepts are classic representatives.

- 3) Overcoming the relationship between doping and conductivity as expressed in the Poisson equation through doping-independent conduction. The two-dimensional electron gas of GaN lateral high electron mobility transistors proves this concept.

#### B. Wide Band-Gap Devices

(1) highlights, with its strong dependency on the critical electric field, the motivation to move into wide band-gap materials. The energy required for band-to-band electron-hole generation through impact ionization is much higher; the breakdown field e.g. in SiC with triple the band-gap (3.26 eV vs. 1.12 eV) is hence nearly a factor of 10 higher compared to silicon (2 MV/cm vs. 0.25 MV/cm). Taking further into account mobility and dielectric constant as expressed in the Baliga Figure-of-Merit (FoM), the limit line for SiC is 231 times below the silicon limit. The same rational applies for one-dimensional vertical GaN devices with a FoM advantage of 2097 [7]. Practically, the channel contribution, contact and substrate resistances, the re-distribution of current (especially in planar gate concepts), and last-but-not-least the ruggedness requirements such as short circuit operation [8] are barriers on the way towards the theoretical limits.

#### C. Two-dimensional Devices (2D)

Two-dimensional devices introduce an electric field component perpendicular to the direction of current flow. Conductivity in the on-state and blocking characteristic are hence no longer coupled through the Poisson equation.

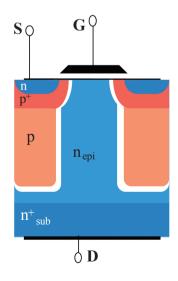

As shown in Fig. 1, Superjunction transistors lower the specific on-state resistance through a compensation structure formed by p-doped pillars placed adjacent to the n-type cur-

Fig. 1. Vertical Superjunction transistor with planar gate structure.

rent conducting regions, thus allowing much higher doping levels in the n-regions.

The p-pillars do not contribute to current conduction in the on-state, but help to maintain the blocking voltage during the off-state by compensating the donor charges in the n-columns. The blocking characteristic depends on the effective doping level, that is, donor charges minus acceptor charges, while the on-state resistance depends on the n-doping level alone. The concept allows therefore an optimization of the area-specific on-state resistance far below the silicon limit. As the adjacent p- and n-columns create a horizontal component of the electric field, an increase of doping level needs to be accompanied by reduction of the cell pitch to stay within the limits of the critical electrical field. The overall electric field is given by a superposition of horizontal and vertical field vectors. The relationship between blocking voltage and  $R_{DS(m)}$ [3] can now be expressed as:

$$R_{on} \cdot A_V = 4 \cdot w \cdot \frac{V_B}{\mu \cdot \varepsilon \cdot E_C^2}.$$

(3)

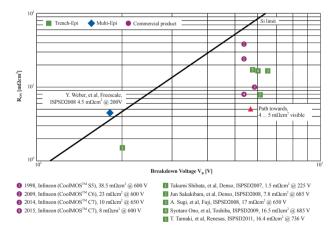

This formula shows a significantly more favorable dependency between on-state resistance and breakdown voltage. Modelling the doping dependence of the critical electrical field in a similar way as described above gives  $R_{on} \cdot A_V \approx V_B^{1.3}$  instead of  $R_{on} \cdot A_V \approx V_B^{2.5}$  as expressed in (2). The direct proportionality to the cell pitch *w*, enables a continuous path towards ever lower on-state resistance. Fig. 2 shows this race towards lower  $R_{on}$  and the hitherto achieved results.

Fig. 2. Specific on-state resistance for different Superjunction devices using Trench Epi and Multi-Epi processes against the limit of silicon.

As the blocking capability of the device depends crucially on the local difference of charges, an elaborate scheme is required to control doping levels both in the p- and n-column precisely during mass production. In order to reduce the on-state resistance below the silicon limit, doping levels in the n-column in the upper  $10^{15}$  cm<sup>-3</sup> to lower  $10^{16}$  cm<sup>-3</sup> range are necessary, whereas a high blocking capability such as 600 V, mandates an effective doping level below 1 to  $2 \cdot 10^{14}$  cm<sup>-3</sup>. The relative difference of charges must be balanced within few percent of their absolute doping levels. A surplus of donor charges turns the drift layer into a lightly n-doped area, a surplus of acceptor charges into a lightly p-doped area. Consequently, with constant doping profiles, the gradient of the vertical electric field changes its sign, moving the point of highest electric field from the top side to the bottom side of the device. Such a characteristic may create instabilities and must be avoided. Hence, constant doping profiles for p-and n-columns are not favorable [9].

In terms of manufacturing technology the subsequent deposition of epitaxial layers with intermediate implantation steps has proven to be compliant both with these needs and has paved a way towards an area specific on-state resistance below 10 m $\Omega$ ·cm<sup>2</sup>. Alternative concepts comprise trench etching and epitaxial re-fill of trenches. In this case grading of doping profiles need to be controlled through the taper angle of the trench.

From our view point refining production technology and device concept will allow further improvements down to an area specific on-state resistance in the range of 4 to 5 m $\Omega \cdot \text{cm}^2$ . Besides production tolerances, early depletion of the current-conducting n-columns may pose a final limit to the Superjunction principle as pointed out by Disney and Dolny [10]. For more background on the history and further use cases of the Superjunction principle, we refer the reader to a recently published article by Udrea *et al.* [11].

The field plate concept is another representative of two-dimensional device concepts. The horizontal field component is created between a metal or quasi-metallic electrode being isolated from the drift region through a thick oxide. Being typically connected to the source electrode, the field plate helps to deplete the n-doped mesa region. Similar to Superjunction transistors, the n-doped region can be significantly higher doped than possible under the limitations of the one-dimensional Poisson equation. Another advantage of the concept is that the field plate shields the gate electrode, which is typically being fabricated within the same trench. The overlap between gate and drain electrode is therefore minimized. The concept is therefore not only beneficial for

Fig. 3. Vertical power MOSFET with field plate.

the on-state resistance, but also for the gate-to-drain capacitance. This makes this structure the preferred technology for power MOSFETs with low to medium breakdown voltages such as 25 V to few hundred volts. Since its introduction the area-specific on-state resistance has been lowered a factor of 50 versus planar silicon power MOSFETs and roughly one order of magnitude versus early implementations of the concept.

Towards higher breakdown voltages the structure is limited by the thickness of the oxide around the field plate, which poses a barrier towards reduction of the pitch and technological challenges. Recent technology analysis has shown that the cross-over point in terms of on-state resistance between field plate and Superjunction concept is located between 300 V and 400 V. Fig. 3 shows the basic structure.

#### D. GaN High Electron Mobility Transistor

The third way to break the limit line of silicon is one of the most challenging but also the most rewarding. Stacking AlGaN on GaN forms a spontaneous charge layer at the interface due to the differences in polarization between the two materials. The charge is confined in the third dimension on the one hand by the bandgap difference at the hetero junction and on the other hand by the band curvature. Hence a two-dimensional charge sheet is created at the interface without any doping in which electrons can move freely. This socalled two dimensional electron gas (2DEG) is the basis for GaN High Electron Mobility Transistors (GaN HEMT). The concentration of the electrons is defined by the mismatch in polarization and can be adjusted through concentration and thickness of the AlGaN barrier.

Contacting this electron gas and controlling the current flow through a gate electrode forms high performance lateral transistors with very high electron mobility and the potential towards unrivalled low area-specific on-state resistance. As the electron gas conducts at zero gate bias, GaN HEMTs yield naturally normally-on transistors. Consequently, effort is required to turn transistors into normally-off or enhancement mode (e-mode) devices as the majority of power electronic applications are voltage source converters. Two major concepts have been commercially introduced to the market: MISFETs, where the AlGaN barrier is locally thinned and the gate electrode is insulated from the 2DEG through a very thin dielectric layer and p-GaN gate transistors having a p-n junction between gate and the 2DEG. The latter concept exists in two variants: the p-GaN gate injection transistor used by Panasonic and Infineon operates with an ohmic contact to the p-GaN gate. It requires a low bipolar current to clamp the gate to a positive forward bias during the on-state of the transistor, but has the unique advantage, that it can tolerate several amperes of forward current thus limiting effectively any voltage spikes on the gate [12]. The second variant of the p-GaN gate concept operates with a Schottky contact to the gate, which yields a low gate current but has issues with a high susceptibility to gate rupture through voltage spikes.

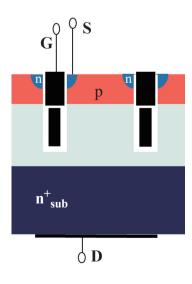

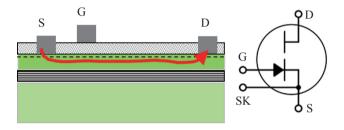

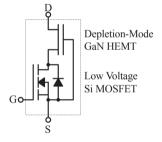

Besides devices showing a normally-off characteristic on

die, also normally-on or depletion mode transistors are commercially available. In this case the transistors are turned into normally-off through a cascode circuit, where a series low voltage MOSFET switches the source of the HEMT with the gate electrode of the HEMT being connected to the source of the LV FET. Even though driving the cascode is easy, we believe that the bigger potential is with e-mode devices. First, the series low voltage MOSFET adds capacitance and complexity deteriorating especially FoMs for charge of the output capacitance; second, power devices require essentially slew rate control. Hence, direct gate access as provided by the e-mode concept is preferred to the indirect switching of the cascode.

Fig. 4 shows an e-mode GaN HEMT and its electric symbol, Fig. 5 shows the cascode circuit.

Fig. 4. Structure of lateral GaN HEMT and electrical symbol of the e-mode GaN HEMT.

Fig. 5. Electric circuit for depletion mode GaN HEMT (cascode).

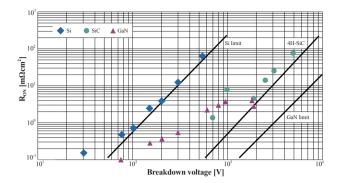

The relationship between on-state resistance and breakdown voltage does not follow the theory for vertical power devices but is much closer to the theory for silicon-on-insulator devices as formulated by Zingg [13]. In case of constant density of the 2DEG, the field distribution along the drift zone can be compared to one-dimensional RESURF devices. Characteristic are two distinct peaks of the electric field at the gate electrode and the drain contact. Further device optimization can therefore follow the ideas developed for lateral RESURF devices [14]. Fitting a curve to published experimental values of  $R_{DS}(on)$  and breakdown voltage suggests a dependency  $R_{ON} \cdot A_V \approx V_B^{1.3}$  similar to the relationship derived for Superjunction transistors. Fig. 6 shows the corresponding graph in comparison to the vertical limit lines of silicon, SiC and GaN, where data points are taken from [7].

Obviously, there is large improvement potential from today's state-of-the-art towards fundamental limit lines making GaN HEMTs a very interesting candidate for significant

Fig. 6. Reported values for area specific on-state resistance for GaN HEMTs and SiC in comparison to material specific limit lines for vertical devices [7].

reduction in terms of  $R_{on} \cdot A$  and cost.

#### III. SWITCHING LOSSES WITH SPECIAL EMPHASIS ON WIDE BANDGAP AND SUPERJUNCTION POWER DEVICES

We will group switching losses into three distinct categories: turn-off losses, turn-on losses, and soft switching losses. We will not consider gate drive losses, as these losses are comparatively small for high voltage devices, being the main scope for this article.

#### A. Turn-off Losses

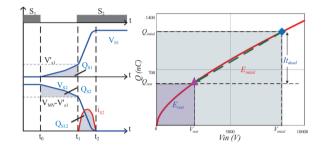

Fast switching power devices, such as Superjunction, GaN HEMT, or SiC devices, are able to come at least close to the theoretical limit of switching losses during turn-off. The minimum turn-off loss being recorded at the terminals as overlap of current and voltage is the energy stored in the output capacitance [15]. In this case, the channel - be it a MOS channel or a bipolar Gate-injection structure such as in e-mode GaN HEMTs - is turned off before the voltage across drain to source rises. The load current commutates into the output capacitance charging it from zero Volts up to the DC link voltage. If this mechanism is lossless - we will see later that this is not entirely true - the energy, observed on the oscilloscope as overlap between voltage and current, equals the energy  $E_{oss}$ , a value which is typically given in the datasheet. It is noteworthy that the energy stored in the output capacitance should be derived from large signal analysis not from small signal due to hysteresis effects especially in Superjunction devices [16], [17].

If we turn-off in this way, physically speaking, no energy is yet dissipated. The current inside the device flows as a capacitive displacement current not as a drift current. That means that the space charge layer inside the device structure builds up by carriers moving away from the boundary of the space charge layer towards the contacts. In case of a Superjunction transistor, electrons will move within the n-columns to the drain, holes will move within the p-columns to the source contact leaving a depleted zone behind. The key point is that these carriers are not crossing any space charge layer. They should always flow as majority carriers within undepleted areas. The turn-off mechanism is hence in the ideal case entirely lossless. The energy stored in the output capacitance is dissipated when the device is turned on under voltage unless an external circuit provides zero voltage switching conditions. The energy stored in the output capacitance is therefore a good indicator on the strength of a power device to achieve low overall switching losses. Especially for hard switching circuits such as Continuous Current Modulation (CCM) for e.g. Power Factor Correction (PFC) applications, improvements in the energy stored in the output capacitance lead directly to corresponding lower overall losses and better efficiency.

Even though fast turn-off is desirable from an efficiency perspective, there are several drawbacks to this concept. There is basically no slew rate control as the voltage rise dv/dt (4) is defined by the load current and the shape of the output capacitance.

$$\frac{dv}{dt} = \frac{I_l}{C_{ass}} \tag{4}$$

Reducing the output capacitance especially on the high voltage end helps to reduce the energy stored in the output capacitance, but makes the device inevitably faster switching. This is especially true for Superjunction devices and GaN HEMTs. Both devices have the capability to switch at a speed of far greater than 100 V/ns.

In abnormal conditions such as an AC cycle drop in a PFC stage or a secondary side short circuit on a LLC converter, very high currents may occur, leading to excessive high dv/ dt. These high slew rates may create issues with EMI or induce parasitic oscillations, which may potentially destroy the power device.

In many cases, the switching speed must be limited. The most effective and most common way is to use a gate resistor, which limits the current for charging and discharging the gate capacitance of the device. Turning off the MOS channel takes a little bit longer. The control is now implemented through the reverse capacitance  $C_{\mbox{\tiny gd}}.$  The slew rate is expressed as (5) with gate current Ig, gate resistor Rg, and Miller plateau voltage  $V_{MP}$ . By varying  $R_g$  the slew rate can be controlled accordingly. During the Miller plateau phase, the voltage across drain to source  $V_{DS}$  rises; the entire gate current flows through the reverse capacitance  $C_{ed}$ , the gate voltage V<sub>GS</sub> does not change. After this plateau, the voltage has reached the DC link voltage and the current starts to fall. The device is controlled in this period by the discharging of the input capacitance below the Miller plateau voltage and the corresponding transconductance of the power device.

$$\frac{dv}{dt} = \frac{I_g}{C_{gd}} = \frac{V_{MP}}{R_g \cdot C_{gd}}$$

(5)

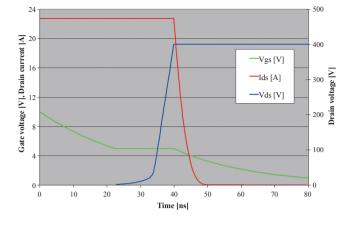

Fig. 7 shows these behaviors in an ideal manner without any parasitics.

Fig. 7. Ideal turn-off of a power device by controlling the turn-off speed by the gate current flowing through the reverse capacitance  $C_{gd}$ .

Ideally, the gate resistor is chosen in such a way, that in normal operation conditions, optimum lossless turn-off is maintained, but at high peak currents both dv/dt and di/dt is controlled. In this way, both safe operation and best efficiency is achieved.

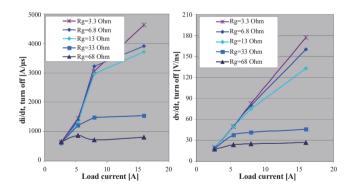

Fig. 8 shows resulting di/dt and dv/dt slew rates as a function of load current and gate resistor for a 190 m $\Omega$  Superjunction device (CoolMOS<sup>TM</sup> CP). Limiting, for example, di/dt below 2000 A/µs and dv/dt below 60 V/ns requires a gate resistor of around 20  $\Omega$ . For load currents below 5 A di/dt and dv/dt is still linearly increasing with load current. Control follows hence the lossless charging of the output capacitance. At higher currents, however, the control is shifted into C<sub>gd</sub> control with corresponding limitations on dv/dt and di/dt.

Fig. 8. Slew rated di/dt (left) and dv/dt (right) as function of load current and gate resistor during turn-off, Superjunction device 600 V / 190 m $\Omega$ .

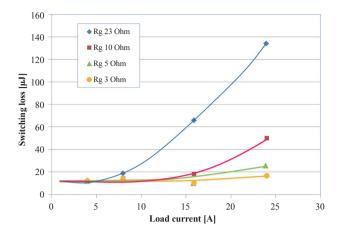

Recent Superjunction generations have been optimized to allow this combined control seamlessly with minimum effect on efficiency. Fig. 9 shows the turn-off losses as function of load current for the latest generation of Superjunction devices (CoolMOS<sup>TM</sup> C7).

As shown in Fig. 9 using, for example, a gate resistor in the range of 10  $\Omega$  allows minimum turn-off losses close to the theoretical limit for a current range up to 15 A.

Fig. 9. Turn-off loss of a 60 m $\Omega$  / 600 V rated Superjunction device as function of current and gate resistor switching against a 6 A SiC Schottky barrier diode.

#### B. Turn-on Losses

Turn-on losses can be divided into two major contributions: one loss source arises from parasitic capacitances of the switching cell circuit, and a second loss source comes from shortening the output capacitance of the power device itself. A switching cell consists fundamentally of the switch, a freewheeling element, and at least an input capacitor. In case of a boost converter the freewheeling element is a diode, preferably a SiC Schottky barrier diode, or in case of a synchronous boost, a power MOSFET such as Superjunction or GaN HEMT. In case of a flyback, the freewheeling element is a synchronous MOSFET or a diode on the secondary side of the transformer.

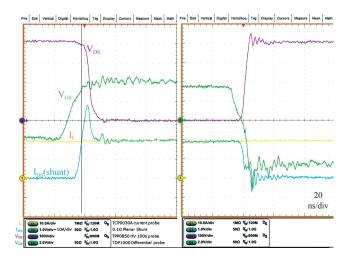

In hard switching conditions the charge of the freewheeling element is added to the load current causing a characteristic current peak. Fig. 10 shows an example of a 70 m $\Omega$ GaN HEMT half bridge device arranged in a symmetric half bridge. Both turn-on and turn-off show very linear di/dt and dv/dt slopes. The turn-off waveform demonstrates perfect shut-off of the channel before the voltage rises, thus bringing

Fig. 10. Turn-on and turn-off waveform of a 70  $m\Omega$  / 600 V rated e-mode GaN HEMT arranged in a symmetric half bridge.

the turn-off loss very close to its theoretical minimum. It is noteworthy, that GaN offers such loss-less turn-off at a time scale of just a few ns.

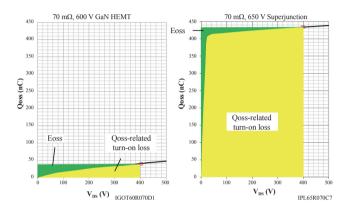

The losses from the freewheeling element amount in total to  $Q_{oss} \cdot V_{DC}$  as a minimum with  $Q_{oss}$  being the charge stored in the output capacitance of the freewheeling element. The distribution of this loss into the device turning on and the freewheeling element respectively is given by the voltage dependency of  $Q_{oss}$ . Whereas Superjunction devices basically deliver the entire  $Q_{oss}$  at very low voltage, GaN HEMTs show a more favorable dependency with losses roughly evenly split between both devices in the half bridge. Fig. 11 shows the  $Q_{oss}$  curves of advanced Superjunction versus an e-mode GaN HEMT.

Fig. 11. Comparison of  $Q_{oss}$  versus voltage for an e-mode GaN HEMT (left) to an advanced Superjunction device (right).

The  $Q_{oss}$  curve represents the losses associated from the freewheeling element as yellow shaded area. These losses can be expressed as:

$$\mathbf{E}_{\text{Qoss}} = \int_0^{V_{DC}} Q_{oss}(V) \cdot dV \,. \tag{6}$$

Similarly, the losses associated with short-circuiting the output capacitance  $E_{oss}$  can be seen as green shaded area in the same graph [18]. Despite GaN HEMTs having nearly a factor 10 lower  $Q_{oss}$  in comparison to Superjunction, the energy  $E_{oss}$  is in the same order of magnitude. The losses originating from  $E_{oss}$  can be expressed as:

$$E_{Eoss} = \int_0^{V_{DC}} C_{oss}(V) \cdot V \cdot dV.$$

<sup>(7)</sup>

The output capacitance should be derived from large signal analysis. The strong non-linear shape of the output capacitance of Superjunction devices leads to a very good optimization of  $E_{oss}$ -associated losses, which is a prerequisite for hard-switching circuits with SiC Schottky barrier diodes or silicon-based ultra-fast diodes as freewheeling elements. GaN HEMTs will in addition also perform perfectly well in symmetrical half bridges, where Superjunction devices can only be used with external circuitry providing zero voltage conditions.

A third contribution of turn-on losses comes from the inevitable overlap of load current with voltage. Assuming constant dv/dt and di/dt slopes these losses can be modeled as:

$$E_{I-V} = \frac{1}{2} \cdot \left( \frac{V_{DC} \cdot \frac{I_L^2}{dI/dt} + I_L \cdot \frac{V_{DC}^2}{dV/dt}}{\frac{1}{2}} \right).$$

(8)

This formula gives an interesting insight into the necessity for fast switching to optimize losses. As long as both di/dt and dv/dt increase linearly with load current, turn-on losses from the overlap of current and voltage will increase only linearly with load current. The efficiency of a power converter with losses only linearly increasing with load is constant. If, however, di/dt or dv/dt needs to be limited, losses will increase parabolically; the converter efficiency will correspondingly decrease as function of load.

It is hence of utmost importance to optimize layout and parasitic inductances of the switching cell to take the maximum benefit of modern power devices with their intrinsic capabilities to reduce switching losses. SMD packages such as TO-leadless or at least packages with separate source bond wire (Kelvin contact) such as 4-pin TO 247 will be mandatory to tap into the performance advantages of modern power devices.

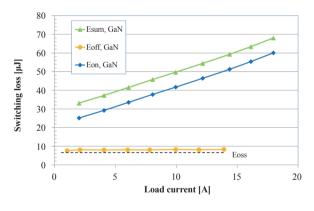

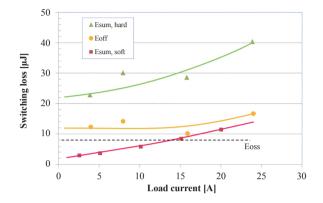

Fig. 12 shows turn-on, turn-off, and sum of switching losses for an e-mode GaN HEMT arranged in a symmetric half bridge.

Fig. 12. Turn-on, turn-off, and sum of switching losses of a 70 m $\Omega$  / 600 V rated e-mode GaN HEMT arranged in a symmetric half bridge.

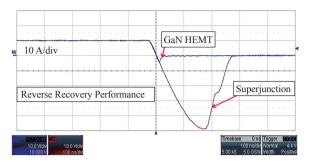

In the considerations above we assumed unipolar current transport in the freewheeling element. This is both true for GaN HEMTs and for SiC Schottky barrier diodes, however false for Superjunction devices. In reverse direction the intrinsic body diode of the device (see Fig. 1) will conduct and will flood the voltage supporting zone with electron hole plasma. In hard switching symmetric half bridges, there will be hard commutation of this conducting body diode. Due to the device structure of Superjunction devices with its deep p-columns, the electron-hole plasma needs to be entirely removed before the device blocks voltage. This effect leads to a very high reverse recovery peak and a snappy discontinuation of the reverse recovery current with very high di/ dt values. Fig. 13 shows a comparison of the hard commutation behavior of a Superjunction device in comparison to an e-mode GaN switch.

Fig. 13. Comparison of the reverse recovery behavior of an e-mode GaN HEMT in comparison to a Superjunction device.

The amount of reverse recovery charge can be reduced through reduction of the ambipolar carrier life time leading to overall lower losses. The device can be made rugged to ensure survival during hard commutation events (e.g. Cool-MOS<sup>™</sup> P7); the snappiness of the body diode however will always remain.

Taking these additional  $Q_{rr}$  losses into account, Superjunction devices are ruled out for symmetric half bridge circuits unless external circuitry is provided for zero voltage switching. We will discuss examples of these circuits in Section IV.

#### C. Perspective of Switching Losses

All power devices discussed in this article, be it based on silicon using field plate, on the Superjunction concept, or on wide bandgap materials, have the possibility to switch at several thousand amperes per microsecond and at dv/dts beyond 100V/ns. Losses arising from the overlap of current and voltage can hence be minimized to limits given by EMI and layout parasitics.

With GaN HEMTs, and to some extent with SiC MOS-FETs, (near)  $Q_{rr}$ -free devices exist.

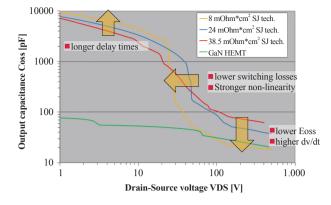

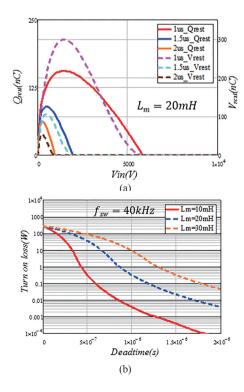

The energy stored in the output capacitance,  $E_{oss}$ , can be reduced further with every technology step. Fig. 14 shows a comparison of the output capacitance of three consecutive technology nodes of Superjunction devices versus an e-mode GaN HEMT.

The continuous race for lower area specific on-state resistance shifts the output capacitance into more pronounced non-linearity with every generation. This trend helps to reduce the energy stored in the output capacitance, yielding lower switching losses and better efficiency in hard switching applications. However, the devices inherently switch faster at the same load current. Furthermore the turn-off delay time, an important feature for resonant applications, increases.

GaN HEMTs show, in comparison, a near linear shape of the output capacitance which is reflected in and extremely linear switching waveform with near constant dv/dt as

Fig. 14. Development of the characteristic output capacitance of three consecutive technology nodes of Superjunction device in comparison to an e-mode GaN HEMT.

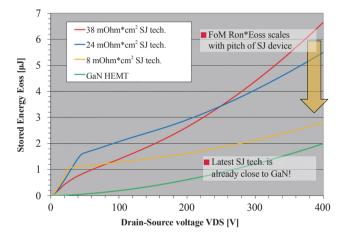

shown in Fig. 10. The comparison of the energy stored in the output capacitance is given in Fig. 15.

Fig. 15. Trend for the energy stored in the output capacitance across three consecutive generations of Superjunction devices in comparison to GaN HEMTs.

The latest generations of Superjunction devices are already reaching the  $E_{oss}$  levels of GaN HEMT devices. With every generation  $E_{oss}$  will further decrease. The path down towards 4 to 5 m $\Omega \cdot cm^2$  will hence coincide with a reduction of the  $E_{oss}$  of another factor of 2. Obviously, improvements in GaN device concept and technology will also result in a lowering of the energy stored in the output capacitance.

The outlook into the primary intrinsic loss mechanism for power device is hence bright both for Superjunction and wide bandgap devices.

All device concepts allow, in hard switching applications, superior performance. Superjunction devices are best when switched against SiC Schottky barrier diodes. Wide bandgap devices, GaN HEMTs and SiC MOSFETs, can be switched in a symmetric half bridge configuration.

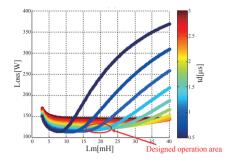

In soft switching applications, where an external circuit ensures zero voltage transition, the sum of turn-on and turn-off losses can be significantly below the  $E_{oss}$  limit. As the turn-off mechanism is, physically speaking, lossless and the

voltage is reduced to zero volts prior to turn on of the device, the only remaining losses are arising from secondary effects such as charging and discharging of internal capacitances and from lumped resistances e.g. in the device contact areas. Fig. 16 shows the sum of hard switching losses versus soft switching losses and the theoretical limit line of  $E_{oss}$  for the latest generation of Superjunction devices.

Fig. 16. Comparison of the sum of soft switching losses versus hard switching losses and the energy stored in the output capacitance,  $E_{oss}$ . 600 V rated device, 60 m $\Omega$ , switching against 6 A SiC Schottky barrier diode.

As long as turn-off losses are constant (up to around 15 A for the 60 m $\Omega$  / 600 V rated device) the sum of soft switching turn-on and turn-off losses stays clearly below the  $E_{\rm oss}$  limit line. The linear increase of losses in this range can be attributed to charging and discharging the output capacitance and reflects increasing losses due to an increasing dv/dt slew rate. Beyond 15 A additional losses from turn-off are added as the channel is now not completely turned off before the voltage across the device rises.

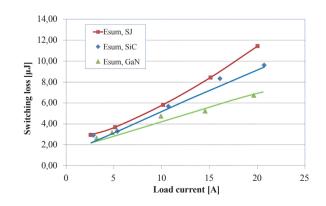

Fig. 17 shows a comparison of round-cycle soft switching losses of Superjunction, GaN HEMT and SiC MOSFET measured with a novel calorimetric approach [19]. The level of loss energies of all device concepts is with a few  $\mu$ J quite similar. The GaN HEMT not only shows the lowest losses but will offer the greatest improvement potential for the future with respect to soft switching losses.

Fig. 17. Comparison of soft switching losses for Superjunction, GaN HEMT and SiC MOSFET, taken from [19].

#### IV. DEVICE CONCEPTS AND THEIR BEST MATCHING APPLICATION CIRCUIT

The key for a true comparison of devices in the application is to choose appropriate circuits and control methods, which bring out the best performance of the individual device concept. As we discussed in the previous sections. Superiunction performs best when switching versus a SiC Schottky barrier diode as freewheeling element. Alternatively, good results are found in zero voltage switching applications at low to medium high switching frequency (30 to 300 kHz). GaN HEMTs can be used in hard switching applications due to their true zero reverse recovery charge. SiC MOSFETs still show some reverse recovery charge even though the ambipolar carrier life time is extremely short. Nevertheless, even for a GaN HEMT the Qoss related charge is roughly a factor 5 higher than the corresponding charge of a SiC Schottky barrier diode. Switching frequencies for hard switching half bridges need hence to be chosen appropriate to keep Qoss related switching losses comparatively low.

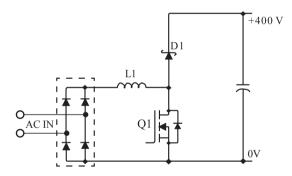

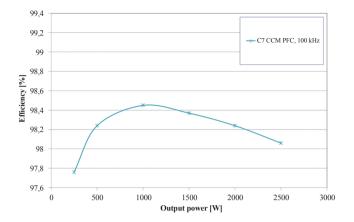

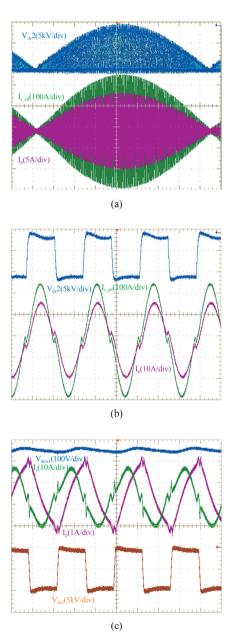

Fig. 18 shows the classic Continuous Current-Mode (CCM) boost stage, which is the prevailing topology for many switch mode power supply applications. As a result, as shown in Fig. 19, a peak efficiency of 98.5% and full load efficiency above 98% is achieved when this circuit is used with the latest generation of Superjunction devices and SiC Schottky barrier diodes.

Fig. 18. Classic continuous current-mode boost stage.

This type of power factor correction stage achieves Platinum or Platinum + level if combined with a well-designed LLC stage including synchronous rectification. If Titanium level needs to be reached, the losses of the bridge rectifier become a major hurdle. Two conducting diodes create at high line (230 V AC) an efficiency drop of around 0.7%. This issue can be overcome with bridgeless topologies, having only one or even no conducting diode in the power flow path.

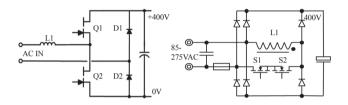

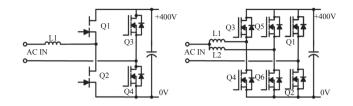

Fig. 20 shows two alternative circuits for bridgeless topologies with only one remaining conducting diode.

Both topologies have only one inductor and two switches. The totem pole has, in the minimum configuration, two slow diodes (D1, D2), but should use another two slow diodes for surge protection. The H4 topology uses two fast diodes (SiC

Fig. 19. Measured efficiency of a CCM PFC stage using a 65 m $\Omega$  Superjunction device in a 4-pin Kelvin contact TO package switching at 100 kHz versus a 16 A rated SiC Schottky barrier diode.

Fig. 20. Bridgeless topologies with only one conducting diode in the power flow path: totem pole (left) and H4 topology (right).

Schottky barrier diodes or ultrafast silicon diodes) and four slow diodes [20]. In the totem pole there is only one diode conducting in the power path. The H4 topology has, during the on-phase of switches S1 and S2, no conducting diode in the power path; during the off-phase of the anti-serial switches, one fast diode and one slow diode conducts. This topology is therefore versatile for low line conditions where the modulation index of switches S1/S2 is high.

When operating in continuous current mode, the totem pole requires switches with very low  $Q_{oss}$  and ideally zero reverse recovery charge. The totem pole therefore works best with GaN HEMTs. The H4 topology can be equipped with Superjunction and SiC Schottky barrier diodes for equally good performance. Forward looking, a bidirectionally blocking and conducting GaN HEMT is an interesting alternative for this topology.

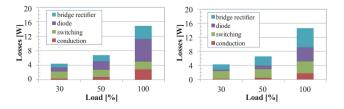

Fig. 21 shows an analysis of the loss contribution from bridge rectifier, freewheeling element, and switches for both topologies.

The loss contribution from the freewheeling element is

Fig. 21. Loss analysis of totem pole (left) and H4 topology (right), 1600 W, 230 V AC in, 65 kHz.

higher in the H4 topology due to higher forward voltage  $V_f$  of the SiC Schottky barrier diode in comparison to the losses of the GaN HEMT conducting in reverse direction in synchronous rectification mode. However, as the slow diode only conducts when switches S1/S2 are off, the contribution from the bridge rectifier is lower in comparison to the totem pole topology. Furthermore, the switching losses in the H4 circuit are lower as the switching losses of a Superjunction device switching against a SiC Schottky barrier diode is lower than of a GaN half bridge circuit operating at the same switching frequency. In total, the efficiency of both topologies is very similar across the entire load range with peak efficiency around 98.8% when operating at 65 kHz.

The totem pole topology can be further improved by replacing slow diodes D1 and D2 with power MOSFETs. This circuit is often referred to as full bridge totem pole. In this case no diode is left in the power flow path. GaN HEMTs are the best choice when operating in continuous current mode. Due to hard switching transients, the losses from both  $Q_{oss}$ and reverse recovery charge do not allow the use of Superjunction devices in this circuit. Therefore, we need to change the control strategy if Superjunction devices should be used in this circuit.

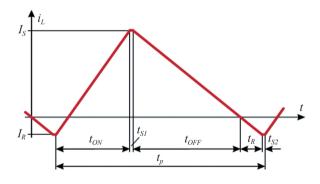

We need to ensure full removal of the reverse recovery charge and ideally discharge the output capacitance before turning on the device to eliminate all associated switching losses. This can be achieved by changing from Continuous Current Mode (CCM) into Triangular Current Mode (TCM) [21] as shown in Fig. 22.

Fig. 22. Triangular current modulation scheme allowing zero voltage switching in half-bridge circuits.

Due to higher peak current from this modulation scheme it is advised to interleave two or more high frequency legs. The resulting circuits for continuous current and triangular current mode are shown in Fig. 23.

In, for example, positive line voltage, a positive current in inductor L1 is built up by turning on switch Q4 (vice versa in inductor L2 by turning on switch Q6). At the desired peak current Q4 is turned off with the current now freewheeling through the body diode of switch Q3, charging the DC link capacitor and returning through Q2. Switch Q3 can now be turned on at any time in a zero voltage condition parallel to the conducting body diode to allow synchronous rectifica-

Fig. 23. Full bridge totem pole circuits using one high frequency leg with GaN HEMT devices in continuous current modulation (left) or two interleaved high frequency legs with Superjunction devices in triangular current modulation (right).

tion. After time interval  $t_{off}$ , the current reaches zero. Keeping Q3 further in the on-state will result in a change of the direction of current flow. Now the current in switch Q3 is positive. Keeping the device on for an interval  $t_R$  with:

$$\frac{1}{2} \cdot I_R \cdot t_R > Q_{rr}(I) \tag{9}$$

ensures complete removal of the reverse recovery charge Qrr from switch Q3. The negative current  $I_R$  furthermore stores energy in inductor L1, which can be used to discharge the half bridge switching node between switches Q3 and Q4 prior to turning on Q4. Zero voltage switching can be achieved, if

$$\frac{1}{2} \cdot L \cdot I_R^2 > Q_{oss}(V) \cdot V_{DC}.$$

<sup>(10)</sup>

It is noteworthy, that for zero voltage switching conditions in half bridge circuits the term  $Q_{oss}*V_{DC}$  needs to be considered and not the energy term  $E_{oss}$  [22]. Referring to Fig. 11 the sum of the yellow and green coloured area needs to be taken into account.

Thus, when both equations are fulfilled, all switching losses related to  $Q_{rr}$  and  $Q_{oss}$  are removed. The devices are now achieving the extremely low soft switching losses as shown in Fig. 16 and Fig. 17 respectively. A peak efficiency above 99.2% has been demonstrated with this type of modulation scheme [23].

Due to the nature of the control scheme, the switching frequency varies strongly with load and across the AC sine wave; between full load / peak AC voltage and light load / zero voltage crossing, the frequency may change up to one order of magnitude. This strong frequency variation may create issues for the control. Furthermore, residual switching losses as shown in Fig. 17, are posing upper limits to the switching frequency.

The frequency swing can be limited by increasing the reverse current time,  $t_R$ , thus trading off switching losses versus additional conduction losses. A combination of partially hard switching and soft switching, thus combining the best aspects of both control schemes, has been proposed to overcome the limits of continuous and triangular current modulation, respectively [24].

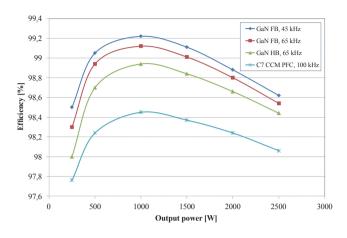

The full bridge totem pole achieves in contrast same or better peak efficiency with great simplicity of control. Fig. 24 shows the measured efficiencies of half bridge and full bridge totem pole configurations.

Fig. 24. Measured efficiencies for various totem pole configurations (half bridge, full bridge) using e-mode GaN HEMTs in comparison to the "classic" CCM PFC stage based on Superjunction and SiC Schottky barrier diode.

With just two 70 m $\Omega$  GaN HEMTs, a peak efficiency above 99% can be achieved in the full bridge totem pole circuit using two additional 35 m $\Omega$  Superjunction devices as low frequency switches. Lowering the switching frequency to 45 kHz allows greater than 99% efficiency from a load range of 20 to 70% of the full load.

Even though we discussed only power factor correction in this section, the underlying concept can be transferred to many applications in power electronics.

#### V. CONCLUSION

The comparison of different power device concepts is only meaningful in combination with their best matching circuits. We showed that both the latest generation of Superjunction devices as well as wide bandgap devices can achieve peak efficiencies above 99% in, for example, non-isolating power factor correction applications. While the control concept for silicon based power devices is more challenging, circuit and control for wide bandgap power devices is relatively simple and straight forward.

Both silicon and wide bandgap power devices have significant potential to further lower on-state resistance and correspondingly the cost of the fabricated die. We showed that Superjunction devices achieve best performance with SiC Schottky diodes as freewheeling element, while wide bandgap devices are very efficient in hard switching half bridge circuits, too.

In soft switching applications, GaN HEMTs with their unique device properties, have the potential towards very high switching frequencies, while silicon-based counterparts are limited to low and moderate switching frequencies.

#### VI. ACKNOWLEDGMENT

I would like to express my gratitude to many colleagues who contributed to aspects of this article. Without their knowhow and support this article would not exist. Special thanks go to Eric Persson and Matteo Kutschak for discussions on the e-mode GaN HEMT and application circuits and to Dr. Oliver Blank for discussions on the field plate concept.

For the provision of accurate measurements on switching losses I am grateful to Dominik Neumayr and Mattia Guacci from the Power Electronics System Laboratory at ETH Zurich.

#### REFERENCES

- F. Udrea, A. Popescu, and W. Milne, "The 3D RESURF Junction," in Proc.10th Int. Symp. Power Semicond. Device ICs, 1998, pp. 141-144.

- [2] G. Deboy, N. Marz, J. P. Stengl, H. Strack, J. Tihanyi, and H. Weber, "A new generation of high voltage MOSFETs breaks the limit line of silicon," *Int. Electron Devices Meet.*, 1998. Tech. Dig., 1998, pp. 683-685.

- [3] T. Fujihira, "Theory of semiconductor superjunction devices," Jpn. J. Appl. Phys., vol. 36, 1997, pp. 6254-6262.

- [4] F. Lee, Q. Li, Z. Liu, Y. Yang, C. Fei and M. M. Mu, "Application of GaN devices for 1 kW server power supply with integrated magnetics", CPSS Transactions on power electronics and applications, vol. 1, no.1, pp.3-12, Dec. 2016.

- [5] C. Hu, "Optimum doping profile for minimum ohmic resistance and high-breakdown voltage," *IEEE Trans. Electron Devices*, vol. 26, no. 3, pp. 243-244, 1979.

- [6] T. Kobayashi, H. Abe, Y. Nimura, T. Yamada, A. Kurosaki, T. Hosen and T. Fujihira, "High-voltage power MOSFETs reached almost to the silicon limit", *Proc.13th Int. Symp. Power Semicond. Device ICs*, 2001.

- [7] T. P. Chow, I. Omura, M. Higashiwaki, H. Kawarada, and V. Pala, "Smart Power devices and ICs using GaAs and Wide and Extreme Bandgap Semiconductors", *IEEE Transactions on Electron Devices*, vol. 64, no. 3, pp. 856-873, Mar. 2017.

- [8] T. Terashima, "Superior performance of SiC power devices and its limitation by self-heating", in *Proc. IEDM*, Dec. 2016.

- [9] G. Deboy *et al.*, "High-voltage semiconductor component," U.S. patent 6,630,698, 1998.

- [10] D. Disney and G. Dolny, "JFET depletion in superjunction devices," in Proc.20th Int. Symp. Power Semicond. Device ICs, 2008, pp. 167-160.

- [11] F. Udrea, G. Deboy, and T. Fujihira, "Superjunction power devices, history, development and future prospects", *IEEE Transactions on Electron Devices*, vol. 64, no. 3, pp. 720-734, Mar. 2017.

- [12] K. Chen, O. Häberlen, A. Lidow, C. Tsai, T. Ueda, Y. Uemoto, and Y. Wu, "GaN-on-Si Power Technology: Devices and Applications", *IEEE Transactions on Electron Devices*, vol. 64, no. 3, pp. 779-795, Mar. 2017.

- [13] René P. Zingg, "On the specific on-resistance of high-voltage and power devices", *IEEE Transactions on Electron Devices*, vol. 51, no. 3, pp. 492-499, Mar. 2004.

- [14] Adrian W. Ludikhuize, "A review of RESURF technology," in Proc.12th Int. Symp. Power Semicond. Device ICs, 2000, pp. 12-18.

- [15] A. Nakajima *et al.*, "Power loss limit in unipolar switching devices: Comparison between silicon superjunction devices and wide bandgap devices," *IEEE Trans. Electron Devices*, vol. 56, no. 11, pp. 2652-2656, 2009.

- [16] J.B. Fedison, M. Fornage, M. J. Harrison, and D. R. Zimmanck, "Coss related energy loss in power MOSFETs used in zero-voltage switched applications", in *Proc. 29th APEC*, Mar. 2014, pp. 150-156.

- [17] J. Roig and F. Bauwens, "Origin of anomolous C<sub>oss</sub> hysteresis in resonant converters with SJ FETs", *IEEE Trans. on Electron Devices*, vol.62, no.9, pp. 3092-3094, Sept. 2015.

- [18] R. Miftakhutdinov, "Analysis and practical method of determining WBG FET switching losses associated with nonlinear Coss", in *Proc. APEC*, 2017, pp. 974-978.

- [19] D. Neumayr, M. Guacci, D. Bortis, and J.W. Kolar, "New calorimetric Power transistor soft switching loss measurement based on accurate temperature rise monitoring", in *Proc. 29th ISPSD*, May 2017.

- [20] D. Tollik and A. Pietkiewicz, "Comparative analysis of 1-phase active power factor correction topologies", in *Proc. INTELEC 1992*, pp. 517-523.

- [21] H. Kapels and G. Deboy, "System and method for controlling a converter", US 8,026,704, 2011.

- [22] M. Kasper, R. M. Burkart, G. Deboy, and J.W. Kolar, "ZVS of Power MOSFETs Revisited", *IEEE Transactions on Power Electronics*, vol. 31, no. 12, pp.8063-8067, Dec. 2016.

- [23] J.W. Kolar, F. Krismer, Y. Lobsiger, J. Mühlethaler, T. Nussbaumer, and J. Miniböck, "Extreme efficiency power electronics", in *Proc. CIPS 2012*, Mar. 2012.

- [24] D. Neumayr, D. Bortis, E. Hatipoglu, G. Deboy, and J. W. Kolar, "Novel efficiency optimal frequency modulation for high power density DC/AC converter systems", in *Proc. of the International Future Energy Electronics Conference*, Jun. 2017.

Gerald Deboy received an M.S. and Ph.D. degree in physics from the Technical University Munich in 1991 and 1996 respectively. He joined Siemens Corporate Research and Development in 1992 and the Semiconductor Division of Siemens in 1995, which became Infineon Technologies later on. He contributed to the development of the CoolMOS<sup>™</sup> technology and its commercial introduction to the market place. From 2004 onward he headed the Technical marketing department for power semi-

conductors and ICs within Infineon Technologies. Since 2009 he is leading a business development group focusing on new fields for power electronics.

He is a Sr. member of IEEE and has served as a member of the Technical Committee for Power Devices and Integrated Circuits within the Electron Device Society. He has authored and coauthored more than 85 papers in national and international journals including contributions to three student text books. He holds more than 60 granted international patents and has more applications pending.

**Oliver Haeberlen** received his M.S. and Ph.D. degree in physics from the University of Munich in 1989 and Technical University of Munich in 1993 respectively.

He joined Infineon Technologies Austria AG (formerly Siemens Semiconductor Branch) in 1995, where he took over responsibility for the process development group of Smart Power Technologies in 1996. In 1998 he became responsible for the process development group of discrete

power transistors (PowerMOS, IGBT, SiC) in Villach, Austria. In 2003 his focus shifted to the development of Infineon's series of low voltage power trench MOSFETs optimized for high frequency and high efficiency switching (OptiMOS<sup>TM</sup>). Since 2010 he is heading the group for advanced technology concepts which evaluates future silicon and wide band gap (SiC, GaN) power device concepts for improved energy conversion solutions.

He is a Sr. member of IEEE and member of the IEEE EDS Power Devices and ICs Technical Committee. He has served as a member of the Technical Program Committee for Power Devices of the IEEE IEDM and ISPSD conferences and was Technical Program Chair for the ISPSD'16 conference. He is author and co-author of over 100 international patents and patent applications in the field of power semiconductors.

**Michael Treu** received his M.E. and Ph.D. degree in electric engineering at the University of Erlangen in 1996 and 1999 respectively. He joined Siemens in 1999, which later became Infineon Technologies. He was part of the team that released the first commercial SiC Power Schottky Diodes in 2001, and is now heading the high voltage MOS development department.

## Review of Power Semiconductor Device Reliability for Power Converters

Bo Wang, Jie Cai, Xiong Du, and Luowei Zhou

Abstract—The investigation shows that power semiconductor devices are the most fragile components of power electronic systems.Improving the reliability of power devices is the basis of a reliable power electronic system, and in recent years, many studies have focused on power device reliability. This paper describes the current state of the art in reliability research for power semiconductor devices, mainly includes failure mechanisms, condition monitoring, lifetime evaluation and active thermal control.Among them, condition monitoring technology are classified and summarized by the failure mechanism and the change rules of characteristic quantities; The method of lifetime estimation isillustrated from the practical point of view;Methods of active thermal control are classified and summarized from the two ideas of reducing loss and loss compensation which are refined by the principle of realization. At last, this paper draws the existing problems and challenges of power devices reliability studies.

*Index Terms*—Active thermal control, condition monitoring, failure mechanism, lifetime evaluation, power device, reliability.

#### I. INTRODUCTION

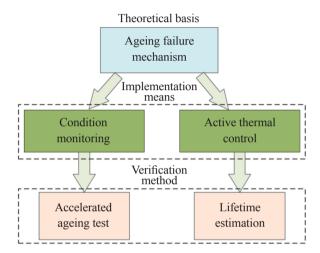

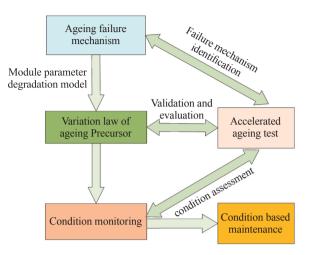

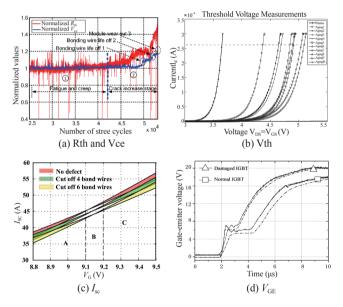

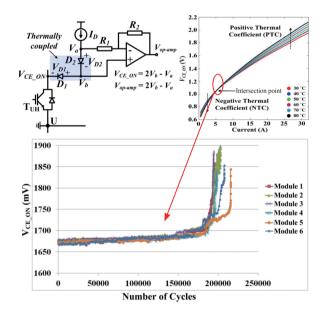

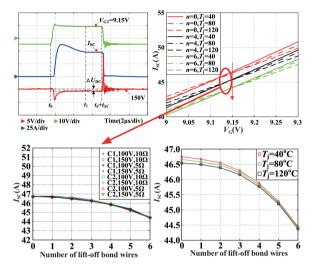

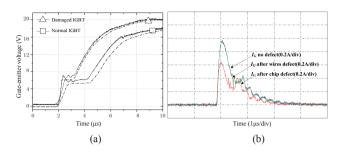

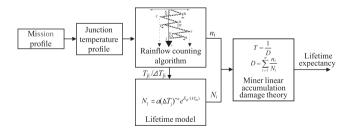

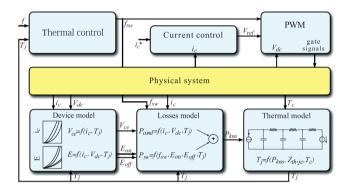

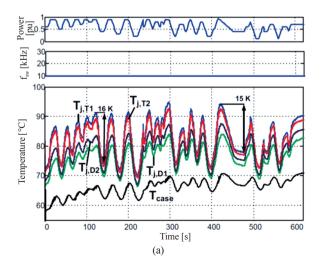

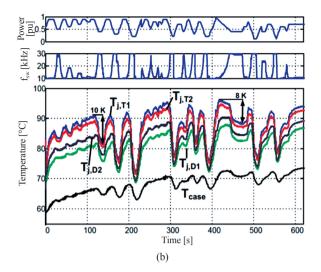

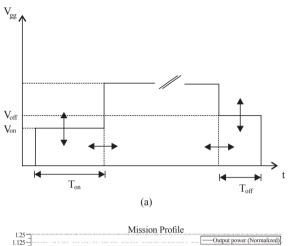

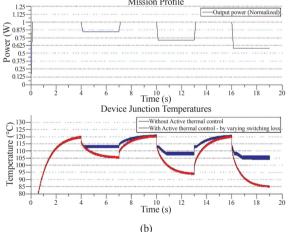

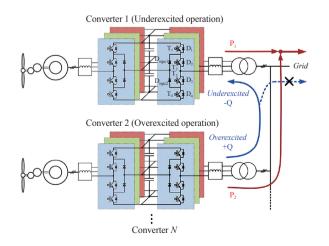

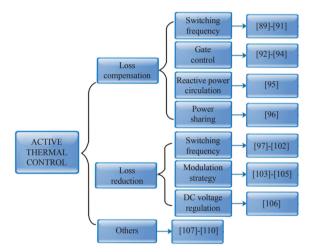

POWER electronic system has high energy conversion efficiency and controllability[1], it has been widely used in aerospace, industrial automation, transportation, renewable energy power generation and other fields which require the highly reliability [2]-[5]. In these fields, the power will fluctuate in a large range [6]-[8], the reliability of power electronic systems with the harsh operating conditions are far less than traditional power equipment. Power semiconductor devices are the core component of power electronic system, and it is also one of the most fragile components in power electronic system [9], so that power device has a significant effect on the reliability of the power electronics system. Thereby, improving the reliability of power devices is one of the focus of power electronics studies. At present, the research on the reliability of power devices mainly includes failure mechanisms, condition monitoring, life estimation and active thermal control etc. As shown in Fig. 1, the study of failure mechanism is the basis of power device reliability research; Condition monitoring and active thermal control

are the implementation means to improve the reliability of power devices; Accelerated aging test and lifetime estimation are the verification methods.

Fig. 1. The main research contents of the reliability of power devices.

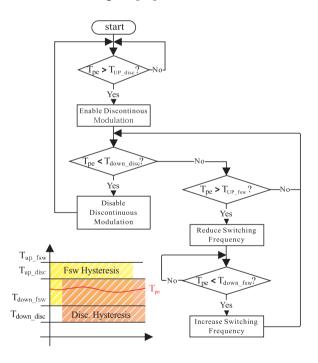

Condition monitoring is one of the implementation means to improve the reliability of power devices, it means the health status of power devices is monitored by characteristic quantities in real-time, it enables timely maintenance to prevent the accident shutdown. The studies of condition monitoring are based on the failure mechanism which can be used to find the characteristic quantities and their change rules, and the change rules can beverified by accelerated aging test. Due to Insulated Gate Bipolar Transistor (IGBT) module is the most widely used in power devices, many studies of converter condition monitoring are mainly around IGBT [10]-[12], a great variety characteristic quantities of IGBT are proposed, the results of these studies are discussed in this paper. Active thermal control is another way to improve the reliability of power devices. The main factors causing aging failure of power devices are thermal stresses which are caused by the means temperature and temperature fluctuations. Active thermal control reduces the means temperature or temperature fluctuations by controlling the loss-related variables, thus reducing the thermal stress of power devices. Although the purpose of active thermal control is to improve the power devices lifetime, active thermal control should take account to the costs involved and make a tradeoff between them.Due to the longer service time of power devices, the feedback of active thermal control from the practical application also longer. Therefore, life estimation is generally used to design active thermal control and verify

Manuscript received June 10, 2017. This work was supported in part by National Natural Science Foundation of China under Grant 51577020 and 51137006, and in part by Chongqing 2015 Graduate Student Research Innovation Project under Grant CYB15034.

The authors are with the School of Electrical Engineering, Chongqing University, Chongqing, China (e-mail: wbo@cqu.edu.cn; caijie\_cee@cqu.edu.cn; duxiong@cqu.edu.cn; zluowei@cqu.edu.cn).

Digital Object Identifier 10.24295/CPSSTPEA.2017.00011

the effect of active thermal control. What's more, customers can obtain the lifetime information by lifetime estimation to proper maintenance; manufacturers can make a new design to increase the lifetime of the power devices by lifetime estimation. The method of lifetime estimation is illustrated from the practical point of view in this paper.

In summary, the studies offailure mechanisms, condition monitoring, lifetime estimation and active thermal control have great significance for improving the reliability of power devices. This paper reviews these studies, Section II summarizes the main failure mechanism and failure modes of IGBT modules; Section III summarizes the current condition monitoring method from different point of view; Section IV summarizes the methods of life estimation and the usage method is illustrated; Section V summarizes active thermal control, refines the basic ideas of active thermal control methods and classifies them accordingly; And section VI draws the conclusions and challenges.

#### II. FAILURE MODES AND MECHANISM OF IGBT MODULES

At present, IGBT modules are widely used in high-power occasions. Its relatively low reliability is mainly attributed to its operation feature of dealing with a wide-range random power fluctuations during a long period.Statistics have shown that power converter is one of the most fragile part of the new energy equipment[2]-[5], among them the IGBT modules are also the most fragile part. The failure modes of it can generally be separated into two categories: chip-related failure and packaging-related failure. The chip-related failure can mainly attributed to the catastrophic failures. In the operation of IGBT modules, transient over-voltage, over-current, electrical-over-stress etc. such causal factors could cause catastrophic failures. However, due to their short transient process, these failures are include in the protection category and excluded from the focus of reliability research.

For silicon chip modules, the current research of the reliability research focus more on the package-related failure. The package structure of IGBT module can also be separated into categories: bonding wire structure and press-packaging structure. Between them, the press pack high-power devices, which have a higher reliability than wire-bond devices, are not discussed in this paper.

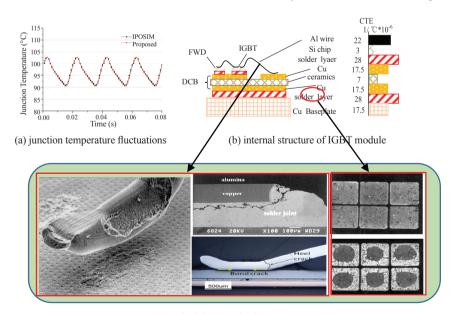

For the typical multi-layers wire-bond module package device as Fig. 2 shown, when the converter deals with a wide range of random fluctuating power, the power fluctuation causes the power device to withstand the shock of thermal cycle for a long time. The temperature fluctuates repeatedly during the thermal cycle. Due to the differences of mechanical and electrical characteristics of multi-layers, most heat loss transfer vertically downward and the temperature gradient arises from top to bottom within the modules resulting in alternating thermal and electrical stress. The alternating thermal and electrical stress and the bending stress of the bond wire itself, resulting in the crack between the aluminum lead and the silicon chip and gradually spread, and eventually lead to bond wire lift off and solder layer fatigue. Therefore, the IGBT internal temperature fluctuations and the unmatched CTE (thermal expansion coefficient) of different materials leading to alternating thermal and electrical stress, is the root cause of ageing failure. Research shows that the fast power cycling (time period is tens of seconds) and higher temperature swing ( $\Delta T > 100$  K) leads to wirebond failure, while the slow power cycling (time periodis several minutes) and lower temperature swing ( $\Delta T < 80$  K) leads to solder fatigue related failures [9].

The failure mechanism of the IGBT modules in the converter mainly includes: bond wire fatigue, aluminum recon-

(c) main failure mechanism

Fig. 2. The internal structure of wire-bond package IGBT modules and main failure mechanism.

struction, solder fatigue and gate oxide degradation [10]. Among them, the aluminum bond fatigue [10], [20] and solder fatigue [21] are the two main failure mechanism of IGBT modules. The aluminum bond wire fatigue including bond wire lift off and heel cracking is caused by the temperature fluctuation and unmatched CTE at the lead-to-chip connection point [12], [22]. The solder layer fatigue refers to the phenomenon of solder cracks and holes under long-term work due to CTE mismatch of the solder connection between the silicon chip and the baseplate [21]. Failures such as solder layer fatigue cracks, cavity and bond wires lifting off or breaking lead to the changes of IGBT thermal, electrical characteristics as well as the degradation of reliability. Thus, failure mechanism is the basis of reliability research of power device.

### III. CONDITION MONTITORING METHODS OF IGBT MODULES

#### A. General Idea of Condition Monitoring Method

Condition monitoring of IGBT modules refers to the process of extracting the information reflecting the health status but without interrupting its normal operation simultaneously. In fact, this process can be achieved by monitoring the operating status, and then determine the health level of the device, and finally evaluate the health condition. Thus, systematic maintenance and optimization repair based on condition monitoring can be achieved.

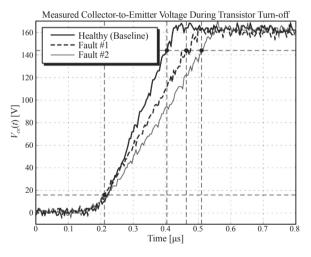

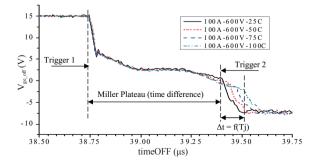

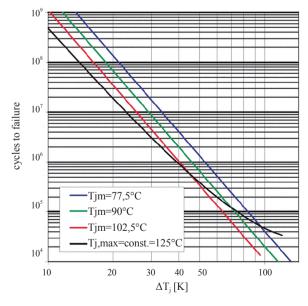

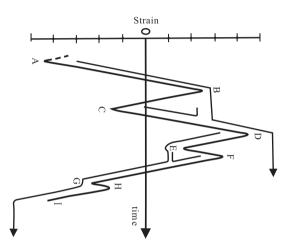

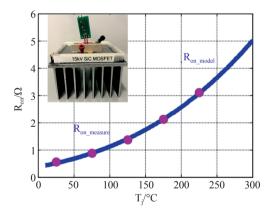

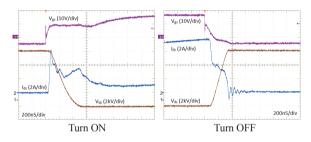

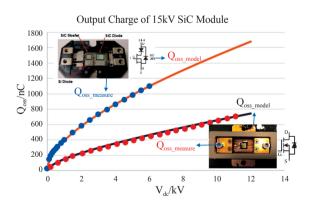

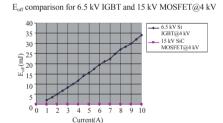

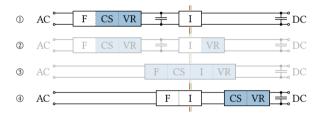

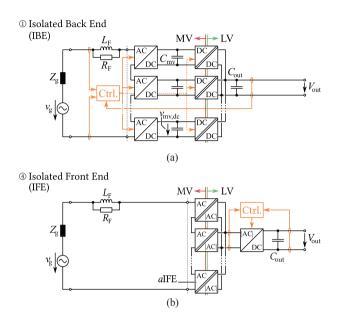

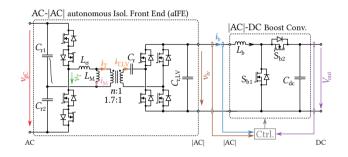

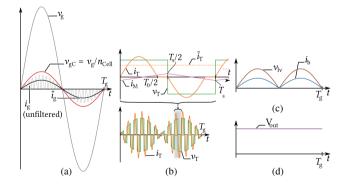

The failure modes of the IGBT modules can be separated into two aspects: sudden failure and aging failure. The sudden failure is instantaneous and unpredictable, belonging to the scope of protection [13]-[15], is not in the discussion of this paper. The ageing failure of IGBT modules are due to long-term work in harsh environment which leading to bear the continuous impact of thermal mechanical stress. Finally, due to the thermal fatigue cumulative damage, the working performance of the module will degrade leading the module parameters or signal shift [16]-[17]. This failure mode is slow and inevitable, if not found in time, will eventually evolve into a catastrophic failure, especially for some high reliability applications will cause incalculable significant losses. Thus, health condition monitoring of the power converter and power devices is of great significance.