# Emerging Trends in Silicon Carbide Power Electronics Design

H. Alan Mantooth, Tristan Evans, Chris Farnell, Quang Le, and Robert Murphree

Abstract—The emergence of wide bandgap power semiconductor devices has opened the possibilities of improved electrical performance and power density. Advanced research into wide bandgap power electronics also includes advances in integrated circuit design, semiconductor device modeling, 3D electronic packaging, and computer-aided design of wide bandgap based electronics. These emerging trends are described along with some early results indicating the additional improvements possible in power density. Operation at extreme temperatures also becomes more feasible.

Index Terms—Gallium nitride, power integrated circuits, power semiconductor devices, power electronics, silicon carbide, wide bandgap semiconductors.

# I. Introduction

Whas become a key enabler for the miniaturization of power electronic systems. This fact has been described and demonstrated in the literature for the past decade or more for many applications. A search of the literature in IEEE Xplore alone reveals over 40,000 articles on wide bandgap related activities alone! Of these, hundreds would be focused on applications exclaiming the virtues of using SiC MOSFETs, JFETs, diodes, SJTs, and IGBTs. Over a similar timeframe investigators at Purdue, Cornell, NASA Glenn, GE, Arkansas, and KTH Stockholm have demonstrated integrated circuitry in silicon carbide (SiC) [1]-[11]. These circuits have been analog, mixed-signal, or digital and have been realized in a variety of technologies including bipolar, JFET, nMOS and CMOS.

A primary motivation for the desire to utilize SiC integrated circuits as opposed to silicon or silicon-on-insulator is revealed in high power density packaging efforts. Attempting to compactly package gate drivers, protection circuits and maybe even controllers with the power devices yields a desire to have circuitry that accommodates the junction temperatures produced by the SiC power devices. In some packaging architectures, shown later in the paper, orienting the gate driver on top of the power device is the ultimate in lower gate-loop and maybe even power-loop inductances to achieve clean switching waveforms. As such, a perfect coefficient of thermal expansion (CTE) match between the two die relieves the stress on the interconnect used

between the power die and the integrated circuit die leading to longer term reliability – a fact that MUST be addressed as part of high power density, heterogeneous integrated design activity.

In order for all-SiC systems to be fully realized, where the term "all" refers to not only the power devices but also the integrated circuitry, several aspects of the design space must be simultaneously considered. These design flow issues will be described in Section II and include optimization, circuit analysis and modeling, as well as board level analysis and modeling. In many higher power systems, it also involves power module design and system assembly design and analysis. All of these issues together constitute a change in design thinking from traditional silicon based power electronics design.

As will be described in Section II, circuit analysis prior to circuit fabrication is an important element in any electronics design process. Circuit analysis relies on accurate models of the components in the circuit in order to produce results that predict the behavior of the circuit under a variety of electrical and environmental conditions. Section III describes the importance of semiconductor device models to the design process.

Section IV describes some of the SiC integrated circuits recently developed for all-SiC power converters and applications. These circuits represent a few of the key functions needed.

# II. DESIGN AUTOMATION FOR SIC SYSTEMS

Power electronics design is becoming increasingly multi-disciplinary with the advent of wide bandgap (WBG) devices. The ability for silicon carbide and gallium nitride devices to switch so fast has brought more simultaneous issues into play in order to fully realize the potential of these more ideal switches. These devices can operate at higher junction temperatures, which promotes higher reliability if proper thermal management is designed in. These devices can switch faster, so they allow the size of passives to decrease. Also, because of the faster switching, circuits are more prone to parasitics that can cause excessive ringing in voltage and current waveforms and unwanted electromagnetic interference generation. So, it is apparent that these WBG technologies promote miniaturization of power electronics [12].

Due to these trends toward higher power density and miniaturization, power electronics is entering a phase of greater integration. And, this integration is increasingly heterogeneous as defined by efforts to embed passives, integrated low-voltage circuitry, and sensors into the same package, board, or module platform with the power semiconductor devices. This integrative activity and the desire of many to optimize the design

Manuscript received September 14, 2017.

The authors are with the Mixed-Signal Computer-Aided Design Laboratory at the University of Arkansas, Fayetteville, AR 72701 USA (e-mail: mantooth@unark.edu)

Digital Object Identifier 10.24295/CPSSTPEA.2017.00016

tradeoffs demands new design automation tools [13]-[15].

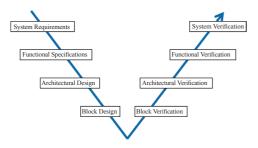

A typical model-based engineering design flow for integrative systems is shown in Fig. 1 [16]. The V-diagram essentially begins in the upper left with the system requirements capture into an executable form. From here the process descends into a partitioned set of subsystems that are successively themselves partitioned and individually designed and verified. The V-diagram is then ascended on the right-hand side to ensure that what was designed meets the subsystem(s) and system specifications. This design approach has been applied to thousands of systems ranging from airplanes to cell phones. Power electronic systems are no different. In fact, as their complexity is increasing, appropriate tools for the various analysis, verification and validation steps required in the V-diagram must evolve or be created.

Fig. 1. The V-diagram design flow that represents a top-down specification and partitioning of a system and a bottom-up verification of the proposed designs. This approach allows for specification negotiation and helps to ensure first-pass success.

In the design flow of Fig. 1, as applied to traditional silicon power electronics in a systems such as more electric aircraft, electric cars, electric ships or hybrid heavy equipment, the typical toolset in today's terms would involve Matlab/Simulink® for some higher-level system analysis, controls development, and even some more idealized circuit analysis (often coupled with the control algorithms). It would involve a SPICE-like simulation tool such as LTSpice<sup>TM</sup>, PLECS®, or Saber® for circuit analysis. Board level layout and analysis would be performed by any number of tools, but most would not typically possess proper signal integrity analysis capabilities Further, if the design called for power modules, then these are taken off the shelf with, at best, some equivalent model of the parasitics associated with the module.

With silicon carbide devices, higher switching frequencies, and higher power densities, this toolset is simply not rich enough. Thermal considerations are a first order concern. Electrical parasitics present in both the power modules and on the printed circuit boards must be accounted for or the circuitry simply may not work. In fact, WBG module design often needs to be tailored to the application to maximize performance and reliability. In the absence of advanced tools, this will lead to a degree of customization that results in expensive design and slow the adoption of the technology.

# A. Circuit Analysis and Modeling

Circuit analysis tools have incrementally evolved over the

past 45 years since SPICE was introduced by UC Berkeley in the 1970s. Clearly, engineers have for decades made due with macromodels and inferior device models for power electronics. The introduction of Saber in the late 1980s began to change this and open up the possibility of having analysis algorithms and models more suited to power electronics [17]. More will be discussed about semiconductor device models in Section III. Some degree of algorithm generalization in terms of integration order and type more ideally suited to periodic sinusoidal systems was introduced in Saber.

Research into switching circuit modeling techniques was also developed through the 1990s as well [18]-[20]. Other research into switching systems simulation was investigated, but found most of its applications in the digital domain [21]. Statespace formulations have been advocated here and there through time, but none seem to find their way to mainstream tools. More recently PLECS has taken hold for power electronics as a commonly used tool. All of these approaches remain viable for WBG design, but perhaps it is time for a new formulation. One that is more dedicated to the nature of switching converters, and is more amenable to the design optimizations that the community seeks to achieve.

A comprehensive description of circuit analysis is a standalone topic for a manuscript or book. The main point to make in the context of this paper is that while the field of circuit analysis has matured, there is room for additional tools that may help to advance the multi-dimensional design tradeoff space that power electronics designers seek to command. A tool that runs fast, gives fairly accurate results, and can account for electrical, thermal, and electromagnetic issues.

## B. Board Level Design and Analysis

One of the major benefits of using SiC devices is the remarkably low switching losses associated with these devices. This is in part due to their significantly faster transition times which minimizes the time in which the device is in the triode region of operation and reduces switching losses. Due to these fast switching characteristics and associated high dv/dt of SiC devices, power electronics designers are now required to factor board parasitics into their design process in a way similar to that of RF and high-speed digital circuit designers. In the past, power electronics designers were accustomed to working with frequencies in the 4 kHz to 20 kHz range with relatively low dv/dt (say 5 kV/μs depending on the device). These relatively slow transients allowed many of the board parasitics to be considered negligible by designers. With the emergence of SiC and other WBG devices, it is now possible, and routinely beneficial, to increase the fundamental switching frequencies from the single kHz range to the 100s of kHz range, and associated dv/ dt transients in the 10-100s of kV/ $\mu$ s range, which allows for capacitors and inductors to be much more effective filters, at the frequency of interest, while also significantly reducing their size and weight. By this same line of reasoning, the once negligible board and trace parasitics can have an overwhelming negative effect on circuitry, and must be analyzed to mitigate adverse effects such as ringing, crosstalk, and conducted or radiated electromagnetic interference (EMI).

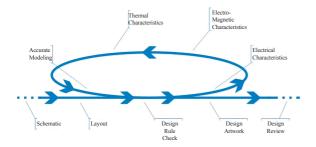

In order to appropriately analyze the effects of board parasitics on the circuits associated with power electronics applications, a new iterative PCB design flow was developed and implemented. Fig. 2 shows the iterative design process currently used in the University of Arkansas (UA) power electronics groups.

Fig. 2. Progression of general design flow illustrating iterative modeling process.

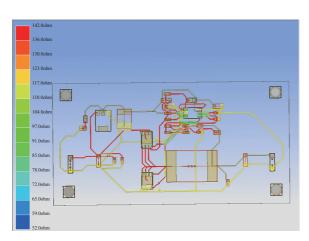

As a first step the circuit schematic is created and simulated using OrCAD<sup>TM</sup> PSpice, LTSpice, or PLECS tools to verify ideal operation. Once basic functionality of the circuit schematic is achieved the printed circuit board (PCB) layout is accomplished using Cadence Allegro<sup>TM</sup>. At this point in the process it is common for power electronics engineers using silicon devices to verify certain "best practices" have been implemented during a design review and have the PCBs be sent out for fabrication. In our design flow we instead continue our analysis by exporting the generated board files to ANSYS SIWave<sup>TM</sup> and perform a parasitic extraction. Fig. 3 shows an impedance scan of a non-ideal PCB layout using SIWave.

Fig. 3. Impedance scan of a non-ideal PCB layout.

Once the parasitic analysis has been completed using SI-Wave<sup>TM</sup> it is then exported to a PSpice circuit library which can then be incorporated into either the original OrCAD simulation or, for more advanced control algorithm evaluation, it may be imported into an OrCAD/Matlab-Simulink co-simulation environment that allows for a coupled controls-circuit simulation of the engineer's design.

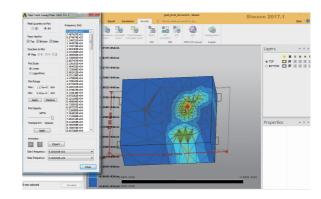

With the circuit now available in the ANSYS tool suite, more advanced analysis may also be performed. The high *dv/dt* and *di/dt* switching characteristics of SiC and other WBG devices contribute significantly to radiated EMI that can adversely affect a product's compliance with FCC standards. It has also been observed that this radiated EMI can cause significant corruption of analog-to-digital converters (ADCs), gate drivers, and even controllers such as digital signal processors (DSPs) that have, in turn, caused catastrophic device failures (Fig. 4). By accurately modeling the circuit's conductive traces, along with high fidelity device modeling, an accurate representation of any transmission paths acting as antennas may be identified and subsequently mitigated. Fig. 5 shows the near-field simulation results for the example non-ideal PCB shown above.

Fig. 4. Destroyed SiC power module (left) and gate driver board (right) due to EMI coupling back into the gate drivers and falsely triggering a power device leading to a shoot-through condition.

Fig. 5. Near field simulation results and frequency window as produced by SIWave.

Once all analyses have been completed for this base iteration, subsequent improvements and iterations are performed until all design specifications are met and the designer has a high confidence interval of success. This iterative process is analogous to the layout, extraction, analysis, and verification approach used in integrated circuit design prior to submission for fabrication.

#### C. Power Module Design

Reiterating, as the state of WBG devices advances, so too must the design and manufacture of power electronic modules in order to achieve greater power density. The higher operating temperature afforded by next-generation power semiconductors can reduce the cooling requirements, thereby reducing the overall size and weight of a system. Likewise, higher switching frequencies offered by these devices directly correlates to a reduction in both the size and weight of system-level passive components [12], [22]. Furthermore, integration of some of these passive components inside the module can have a profound impact on power density. For example, incorporation of decoupling capacitors allows for low impedance paths for parasitic current oscillation, mitigating some of the drawbacks of high frequency operation [23]. However, there are several limitations of conventional packaging techniques that are hindering the adoption of WBG devices. This includes not only the physical limitations of the materials chosen for packaging, but also geometrical considerations that a designer must carefully consider.

Among some of the most profound issues a power module designer faces are those related to parasitic inductance. These stray inductances in both the commutation and gate-source loops of power modules can cause several problems. The high operating frequency of WBG devices along with their high slew rates can lead to scenarios where a high *di/dt* leads to large voltage overshoots during switching transients. This overshoot reduces the safe operating area of the module and is a contributor to EMI issues [22], [24]. Additionally, gate-loop inductance limits the gate-source voltage rise and fall times which, in turn, increases transient duration and switching losses [25]. These can sometimes even end in catastrophic failure of the module as seen in Fig. 4.

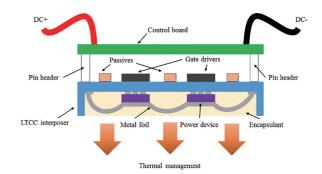

This high *di/dt* and *dv/dt* associated with the fast switching of WBG devices is a major contributor to conducted and radiated EMI. Any methods employed to reduce stray parasitics in the module will have a direct impact on this. Research in this area by incorporating 3D packaging techniques has shown reduction in EMI as well as the benefits associated with a 3D structure. These include higher power density and the possibility for double-sided cooling [22], [26], [27]. Fig. 6 shows an example of a next-generation 3D, wire bondless module.

While the attractive thermal properties of WBG devices offer the possibility of higher device reliability and thermal capability, this does not guarantee the reliability of the system around these devices. Therefore, high reliability at high operating temperature is a crucial consideration. High temperature relates directly to system reliability in the form of failure mechanisms such as die attachment fatigue or bondwire cracking due to power and thermal cycling under harsh operating conditions [28], [29]. Delamination of direct-bonded copper (DBC) during extreme temperature cycling is another well-known failure mechanism that can be mitigated using the step-edge approach for the copper trace to reduce the thermal stress [30]. Undoubtedly, mitigation of these failure mechanisms will improve the

reliability of the overall system. Therefore, detailed analysis is essential in the design phase.

Fig. 6. A 3D power device and gate driver arrangement that significantly reduces generated EMI.

Due to the multidisciplinary nature of power module design, the abovementioned design objectives must be analyzed simultaneously in the design process. Presently, state-of-the-art methods employing high fidelity numerical simulations in an iterative loop are used to simultaneously analyze and synthesize reliable power module designs [31], [32]. While such techniques ensure high accuracy, they are usually computationally expensive, increasing evaluation time and reducing design flexibility. Alternatively, early work in [33] has employed thermal simulations along with lifetime analysis in a response surface based multi-objective optimization routine. This has reduced the number of simulations needed in search of an optimized design. Furthermore, the work in [34] has used strategies borrowed from VLSI work to develop an efficient automated design algorithm. An approach from [35] has shown fast and accurate design by employing reduced order modeling in an optimization loop. Most recently, the work in [36] has allowed more flexible parametric design using thermal resistance networks and closed form equations for both thermal and mechanical analysis. Overall, the abovementioned efforts for CAD tools, models, and algorithms have shown a promising future for a mature design automation flow for power electronic modules – even those that would be heterogeneously integrated with drivers, protection circuits, sensors, and passives where appropriate.

# D. System Assembly Design and Analysis

One of the existing gaps in design automation for power electronics is cabinet-level design. Once the boards, modules, and subsystems are designed, then the task of design and layout of the cabinet is required. This includes electrical and thermal considerations as well as relevant standards pertaining to the application space such as industrial drives, electric grid, and automotive. Best practices and design tools have been identified as a need by engineers in the switchgear industry in particular.

#### III. SEMICONDUCTOR DEVICE MODELING

One of the emerging trends in SiC power electronics is the development of low-voltage SiC circuitry to be packaged with the SiC power die. One of the keys to being able to realize

accurate simulations of SiC circuits is accurate semiconductor device models. This is true for the power electronic circuit analysis [37], [38] as well as the low-voltage circuitry.

Designing integrated circuits depends heavily on the transistor models. Much effort is spent creating models that reflect all of the key characteristics of the transistors used in IC design. The models are typically charge-conserving so that all charges and resulting nonlinear capacitances are accurately modeled over bias and temperature. The models are typically non-quasi-static and capture the effects of bandgap voltage, mobility, and a host of observed physical phenomena [39]. The models are geometry scalable and temperature scalable within a certain regime. And, statistical and variability behavior is modeled so that Monte Carlo analysis and process corner evaluations can be performed in order to center and tolerance the designs. This level of precision engineering is necessary to create the applications we enjoy today in communications, consumer electronics, and computing. The power electronics industry does not enjoy this level of sophistication in its design procedures and levels of automation as outlined in the previous section. And, until WBG power electronics came along, one could argue it was not necessary for most applications. That situation is changing however.

Several generations of silicon transistor models have been created by a number of groups around the world as process technology marched from barely submicron to nanometer scales. Some of the most oft-used of these models are the Berkeley Short-channel IGFET Models (BSIM).

In the IC design world, the industry came together to stan-

dardize on compact models as these transistor models are known. After some investigation, the UA device modeling team chose the BSIM4 standard model to make modifications to in order to create a low-voltage SiC MOSFET model for both n and p type devices [40]. This new model known as BSIM4SIC has all of the features of BSIM4, but with appropriate modifications for SiC. The enhancements which are related to the SiC MOSFET are implemented in the Verilog-A version of the BSIM470. Those enhancements include:

- Non-silicon substrate and non-SiO<sub>2</sub> gate dielectric model using the model flag MTRLMOD. Assigning 1 to the parameter activates the new model,

- A new mobility model that includes the effects of Coulomb scattering resulting from the presence of interface trapped charge. The model can be selected by assigning 3 to the model parameter MOBMOD,

- Trap assisted leakage current modeling of the junction diodes.

- A new definition of effective gate-to-source voltage for the C-V model,

- Effective oxide thickness model for high-κ gate dielectric, electric and physical oxide thickness model to take into account the effects of process variation,

- A charge centroid model for quantum mechanical tunneling of inversion carriers into the oxide,

- A new temperature dependent bandgap model,

- Enhancement of the threshold voltage shift model due to pocket implant,

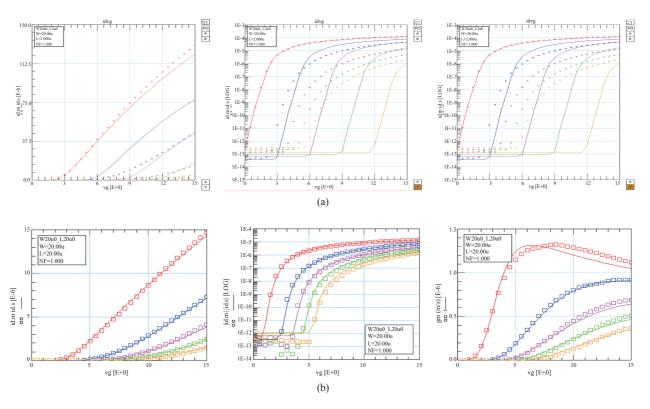

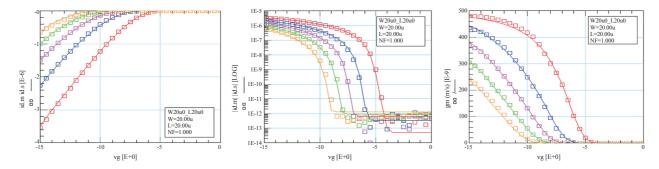

Fig. 7. The best fit curves for BSIM4 against nFET measured data illustrating the body effect (top curves left to right): drain current vs. gate voltage for various back gate voltages at low  $v_{ds}$ ; drain current vs. gate voltage at high  $v_{ds}$ ; transconductance  $(g_m)$  vs. gate voltage. The same curves for BSIM4SIC illustrating how well the new model can be fit to the measured data because it possesses the correct physics.

Fig. 8. The best fit curves for BSIM4SIC against pFET measured data illustrating the body effect (top curves left to right): drain current vs. gate voltage for various back gate voltages at low  $v_{ds}$ ; drain current vs. gate voltage at high  $v_{ds}$ ; transconductance  $(g_m)$  vs. gate voltage.

- A new body effect model,

- A new soft saturation (transition from triode to saturation) model,

- A new channel length and temperature dependent zero bias mobility model, and

- A new temperature scaling model.

Many of these effects including flat band voltage shift, mobility reduction, non-monotonic temperature behavior, soft velocity saturation, and the non-silicon-like body effect can be traced to interface trapped charge in SiC devices.

The results given in [40] show exhaustively how the new model compares to measured data and previous model versions. One example for illustration is the body effect modeling. Fig. 7 shows the best fit for the traditional BSIM4 model to the measured data of SiC devices and the fit for BSIM4SIC in part b. These results are for an nFET device, but similar results were obtained for a pFET (Fig. 8). These sample curves provide insight into the importance of the transistor models for IC design activity and are another example of a design automation component required to effectively pursue all-SiC power converters.

# IV. SiC Integrated Circuit Design

The maturity of traditional silicon power process technologies has led to the nearly complete realization of silicon's potential. Fundamental limitations of silicon prevent it from keeping pace with the power electronics industry's growing demand for increasing power density and concomitant higher operating temperatures. As a result, there has been a notable market shift towards SiC and GaN power devices. These wide bandgap materials are advantageous in power electronics applications due to offering higher critical electric fields and thermal conductivity compared to silicon.

While SiC power devices are commercially available, the corresponding control and protection circuitry is currently silicon based. This introduces a limiting factor for the efficient operation of power modules, particularly at high temperatures since silicon and silicon-on-insulator (SOI) based devices are limited to approximately 125 °C and 250 °C, respectively [41], [42]. To operate in high temperature environments without a significant degradation in product lifetime, these circuits require dedicated cooling solutions that increase costs and add parasitic elements.

To realize the potential of wide bandgap power devices, packaging techniques and integrated circuitry must be developed with similar operational capabilities. With demonstrated operation at temperatures exceeding 300 °C, SiC CMOS ICs represent a viable approach to meeting these requirements [6]-[9]. Flip-chip packaging techniques allow for the realization of a 3D wire bondless power module in which the SiC CMOS gate driver, power management, and protection ICs connect to a power device using solder balls and an interposer. This reduces parasitic elements, yielding the potential for higher switching frequencies along with improved efficiency and reliability.

# A. SiC Gate Driver

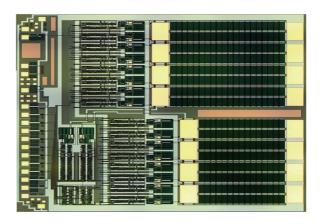

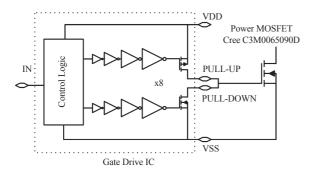

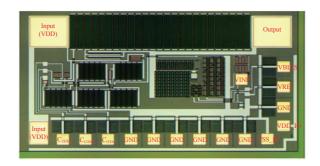

The SiC CMOS gate driver shown in Fig. 9 and presented in [6] has achieved operation above 400 °C with sinking and sourcing capabilities of 8 A and 4 A, respectively. As shown in Fig. 10, the design enables an adjustable drive strength by implementing multiple output stage splices that can allow for higher efficiencies when driving smaller loads. A fault detection feature was also incorporated due to yield issues experienced in previous SiC IC fabrication runs.

# B. SiC Power Management and Protection Circuitry

The development of a SiC gate driver with features comparable to a commercially available silicon based counterpart will

Fig. 9. A die micrograph of the SiC CMOS gate driver fabricated in the HiTSiC® process.

Fig. 10. The schematic of the SiC CMOS gate driver fabricated in the HiTSiC® process.

require an integrated voltage regulator and protection circuitry. The SiC CMOS linear regulator shown in Fig. 11 was designed and fabricated in the same process as the gate driver and is functional at over 400 °C [9]. The regulator provides an output voltage of 15 V from an input voltage of 20 V to 30 V and achieves a continuous output current of 100 mA. An all-NMOS SiC UVLO design has also been presented in [43] and provides a template for the necessary protection circuitry.

Fig. 11. A die micrograph of the SiC CMOS linear regulator fabricated in the HiTSiC® process.

# C. Extending the State of the Art SiC IC Technology

A foundation of SiC CMOS designs has been established with a multitude of mixed-signal circuitry including op-amps, bandgap references, and data converters [8], [44]. More complex designs will be formed by building upon the experience gained in previous design and testing phases. In the case of op amps, for example, a shift towards a higher gain architecture such as the recycling folded cascode [45] will improve the load regulation of the linear regulator. This enhances the precision of the regulator output voltage for a given range of load currents, which can be critical in power electronics applications.

An offset cancellation scheme is another key to the progression of SiC ICs. By implementing this in conjunction with the op amp and bandgap reference in a linear regulator, a temperature stable output voltage can be achieved. The culmination of these efforts creates a path to a fully integrated, intelligent gate driver that provides functionality similar to commercially available silicon based parts while breaking the barriers to even greater power density.

# V. Conclusion

Economy and performance are benefits that come with high power density power electronics, just as in the case of integrated circuit electronics. High density power electronics require the heterogeneous integration of disparate technologies including power semiconductor devices, driver, protection and control circuitry, passives and voltage isolation techniques. One of the keys to advancing power electronic integration has been the commercial reality of wide bandgap power semiconductor devices.

This paper described some of the key emerging trends in SiC power electronics design. One of these trends is in design automation tools for module and board layout, device modeling, parasitic extraction, and verification techniques to address fast switching WBG technologies. Gaps indeed exist in the power electronics design automation space, and advances will be needed to maximize performance. Another trend is wide bandgap integrated circuitry. While this paper focused on SiC, there are efforts on GaN IC design to couple it with GaN devices [46]. A key enabler for WBG IC design is semiconductor device modeling for low-voltage devices. This is another emerging trend [47], [48]. The ability to design and manufacture wide bandgap integrated circuits as drivers, controllers, and protection circuitry allows them to be packaged in close proximity to the power device die to minimize parasitics that would adversely impact system performance. More 3D packaging approaches are likely to be demonstrated as part of the effort to achieve low-inductance, high power density electronics.

## REFERENCES

- J. W. Xie, J. A. Cooper, and M. R. Melloch, "Monolithic NMOS digital integrated circuits in 6H-SiC," *IEEE Electron Device Lett.*, vol. 15, no. 11, pp. 455-457, Nov. 1994.

- [2] S. Ryu and K. T. Kornegay, "Design and fabrication of depletion load NMOS integrated circuits in 6H-SiC," in *Inst. Phys. Conf.*, ch. 4. London, U.K., 1996, pp. 789–792.

- [3] J.-S. Chen, K. T. Kornegay, and S.-H. Ryu, "A silicon carbide CMOS intelligent gate driver circuit with stable operation over a wide temperature range," *IEEE J. Solid-State Circuits*, vol. 34, no. 2, pp. 192-204, Feb. 1999.

- [4] P. Neudeck, M. Krasowski, and N. Prokop, "(Invited) Assessment of durable SiC JFET technology for +600° to -125° integrated circuit operation," ECS Trans., vol. 41, no. 8, pp. 163-176, Oct. 2011.

- [5] C. P. Chen and R. Ghandi, "Designing silicon carbide NMOS integrated circuits for wide temperature operation," in 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, pp. 109-11, 2015.

- [6] M. Barlow, S. Ahmed, H. A. Mantooth and A. M. Francis, "An integrated SiC CMOS Gate Driver," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2016, pp. 1646-1649.

- [7] S. Roy, R. C. Murphree, A. Abbasi, A. Rahman, S. Ahmed, J. A. Gattis, A. M. Francis, J. Holmes, H. A. Mantooth, and J. Di, "A SiC CMOS digitally controlled PWM generator for high-temperature applications," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 10, pp. 8364-8372, Oct. 2017.

- [8] A. Rahman, L. Caley, S. Roy, N. Kuhns, A. Mantooth, J. Di, A. M. Francis, and J. Holmes, "High Temperature Data Converters in Silicon

- Carbide CMOS," *IEEE Transactions on Electron Devices*, vol. 64, no. 4, pp. 1426-1432, Apr. 2017.

- [9] R. C. Murphree, S. Ahmed, M. Barlow, A. Rahman, H. A. Mantooth, and A. M. Francis, "A CMOS SiC linear voltage regulator for high temperature applications," in *International Conference on High Temperature Electronics (HiTEC)*, vol. 2016, pp. 106-111, Jan. 2016.

- [10] S. Kargarrazi, L. Lanni, S. Saggini, A. Rusu and C. M. Zetterling, "500 °C bipolar SiC linear voltage regulator," *IEEE Transactions on Electron Devices*, vol. 62, no. 6, pp. 1953-1957, Jun. 2015.

- [11] R. Hedayati, L. Lanni, A. Rusu and C. M. Zetterling, "Wide temperature range integrated bandgap voltage references in 4H–SiC," *IEEE Electron Device Letters*, vol. 37, no. 2, pp. 146-149, Feb. 2016.

- [12] H. A. Mantooth, M. D. Glover, and P. Shepherd, "Wide bandgap technologies and their implications on miniaturizing power electronic systems," *IEEE Journal on Emerging and Selected Topics in Power Electronics*, vol. 2, no. 3, pp. 374-385, Sept. 2014.

- [13] T. M. Andersen, F. Krismer, J. W. Kolar, T. Toifl, C. Menolfi, L. Kull, T. Morf, M. Kossel, M. Brändli, and P. A. Francese, "Modeling and pareto optimization of on-chip switched capacitor converters," *IEEE Trans. on Power Electronics*, vol. 32, no. 1, pp. 363-377, Jan. 2017.

- [14] R. M. Burkart, J. W. Kolar, "Comparative eta-rho-sigma pareto optimization of Si and SiC multilevel dual-active-bridge topologies with wide input voltage range," *IEEE Trans. on Power Electronics*, vol. 32, no. 7, pp. 5258-5270, Jan. 2017.

- [15] N. R. Mehrabadi, Q. Wang, R. Burgos, and D. Boroyevich, "Multi-objective design and optimization of a vienna rectifier with parametric uncertainty quantification," in *IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL)*, pp. 1-6, Jul. 2017.

- [16] P. R. Wilson and H. A. Mantooth, Model Based Engineering of Complex Electronic Systems, Elsevier Publishers, London, England, 511 pgs., March 2013.

- [17] H. A. Mantooth and M. Vlach, "Beyond SPICE with saber and MAST," *IEEE Proc. of Int. Symposium on Circuits Syst.*, vol. 1, pp. 77-80, May 1992.

- [18] J. Sun, R. M. Bass, "Modeling and practical design issues for average current control," in 14th Applied Power Electronics Conference (APEC), pp. 980-986, 1999.

- [19] C. Sun, B. Lehman, and J. Sun, "Ripple effects on small-signal models in average current mode control," in 15th Applied Power Electronics Conference (APEC), pp. 818-823, 2000.

- [20] J. Sun and H. Grotstollen, "Symbolic analysis methods for averaged modeling of switching power converters," *IEEE Trans. on Power Electronics*, vol. 12, no. 3, pp. 537-546, Mar. 1997.

- [21] D. Bedrosian, J. Vlach, "Time-domain analysis of networks with internally controlled switches," *IEEE Trans. Circuits Syst. I – Fundamental Theory and Appl.*, vol. 39, no. 3, pp. 199-212, Mar. 1992.

- [22] S. Seal and H. Mantooth, "High performance silicon carbide power packaging—Past trends, present practices, and future directions," *Energies*, vol. 10, no. 3, p. 341, 2017.

- [23] Z. Chen, Y. Yao, D. Boroyevich, K. D. T. Ngo, P. Mattavelli, and K. Rajashekara, "A 1200-V, 60-A SiC MOSFET multichip phase-leg module for high-temperature, high-frequency applications," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2307-2320, 2014.

- [24] S. Tanimoto and K. Matsui, "High junction temperature and low parasitic inductance power module technology for compact power conversion systems," *IEEE Trans. Electron Devices*, vol. 62, no. 2, pp. 258-269, 2015.

- [25] Z. Liang, P. Ning, F. Wang, and L. Marlino, "Reducing parasitic electrical parameters with a planar interconnection packaging structure," in 7th Int. Conf. Integr. Power Electron. Syst., vol. 9, pp. 374-379, 2012

- [26] A. Dutta and S. S. Ang, "Electromagnetic interference simulations of power electronic modules," in *IEEE International Workshop on Inte*grated Power Packaging, IWIPP 2015, vol. 4, no. 3, pp. 83-86, 2015.

- [27] A. Dutta and S. S. Ang, "Electromagnetic interference simulations for wide-bandgap power electronic modules," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 4, no. 3, pp. 757-766, 2016.

- [28] M. Ciappa, "Selected failure mechanisms of modern power modules," *Microelectron. Reliab.*, vol. 42, no. 4-5, pp. 653-667, 2002.

- [29] G. Bower, C. Rogan, J. Kozlowski, and M. Zugger, "SiC power electronics packaging prognostics," in *IEEE Aerosp. Conf. Proc.*, 2008.

- [30] P. Ning, R. Lai, D. Huff, F. F. Wang, K. D. T. Ngo, V. D. Immanuel, and J. K. Karimi, "SiC wirebond multichip phase-leg module packaging design and testing for harsh environment," *IEEE Trans. Power Electron.*, vol. 25, no. 1, pp. 16-23, 2010.

- [31] N. Hingora, X. Liu, B. McPherson, Y. Feng, and H. A. Mantooth, "Concerning layout synthesis for power electronic multi-chip modules," in 2010 IEEE 12th Work. Control Model. Power Electron. COMPEL, 2010.

- [32] U. Drofenik, D. Cottet, A. Muesing, and J. W. Kolar, "Design tools for power electronics: Trends and innovations," *Ingénieurs de l'automo-bile*, no. 791, pp. 40-47, 2007.

- [33] B. Ji, X. Song, E. Sciberras, W. Cao, Y. Hu, and V. Pickert, "Multi-objective design of IGBT power modules considering power cycling and thermal cycling," *IEEE Trans. Power Electron.*, vol. 8993, no. c, p. 1, 2014

- [34] P. Ning, F. F. Wang, and K. D. T. Ngo, "Automatic layout design for power module," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 481-487, 2013.

- [35] B. W. Shook, A. Nizam, Z. Gong, A. M. Francis, and H. A. Mantooth, "Multi-objective layout optimization for multi-chip power modules considering electrical parasitics and thermal performance," in 2013 IEEE 14th Workshop on Control and Modeling for Power Electronics, COMPEL, 2013.

- [36] L. M. Boteler and S. M. Miner, "Power packaging thermal and stress model for quick parametric analyses," in *Proceedings of the ASME* 2017 International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems Inter-PaCK, pp. 1-8, 2017.

- [37] H. A. Mantooth, K. Peng, E. Santi, and J. L. Hudgins, "Modeling of wide bandgap power semiconductor devices – Part I," *IEEE Trans. on Electron Devices*, vol. 62, no. 2, pp. 423-433, Feb. 2015.

- [38] E. Santi, K. Peng, H. A. Mantooth, and J. L. Hudgins, "Modeling of wide bandgap power semiconductor devices – Part II," *IEEE Trans.* on *Electron Devices*, vol. 62, no. 2, pp. 434-442, Feb. 2015.

- [39] W. Liu and C. Hu, BSIM4 and MOSFET Modeling for IC Simulation, World Scientific, 2011.

- [40] S. Ahmed, Modeling and Validation of 4H-SiC Low Voltage MOS-FETs for Integrated Circuit Design, Ph.D. Dissertation, 297 pgs., Dept. of Electrical Engineering, University of Arkansas, Dec. 2016.

- [41] H. Kappert, N. Kordas, S. Dreiner, U. Paschen, and R. Kokozinski, "High temperature SOI CMOS technology and circuit realization for applications up to 300°C," in 2015 IEEE International Symposium on Circuits and Systems (ISCAS), 2015, pp. 1162-1165.

- [42] J. M. Hornberger, E. Cilio, R. M. Schupbach, A. B. Lostetter, and H. A. Mantooth, "A high-temperature multichip power module (MCPM) inverter utilizing silicon carbide (SiC) and silicon on insulator (SOI) electronics," in *Power Electronics Specialists Conference*, 2006. PESC '06. 37th IEEE, Jeju, S. Korea, 2006, pp. 1-7.

- [43] M. D. Glover, P. Shepherd, A. M. Francis, M. Mudholkar, H. A. Mantooth, M. N. Ericson, S. S. Frank, C. L. Britton, L. D. Marlino, T. R. McNutt, A. Barkley, B. Whitaker, and A. B. Lostetter, "A UVLO circuit in SiC compatible with power MOSFET integration," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 2, no. 3, pp. 425-433, Sept. 2014.

- [44] A. Rahman, P. D. Shepherd, S. A. Bhuyan, S. Ahmed, S. K. Akula, L. Caley, H. A. Mantooth, and J. Di, "A family of CMOS analog and mixed signal circuits in SiC for high temperature electronics," in 2015 IEEE Aerospace Conference, Big Sky, MT, 2015, pp. 1-10.

- [45] R. S. Assaad and J. Silva-Martinez, "The recycling folded cascode: A general enhancement of the folded cascode amplifier," in *IEEE Jour*nal of Solid-State Circuits, vol. 44, no. 9, pp. 2535-2542, Sept. 2009.

- [46] Navitas Semiconductor. [Online]. Available: https://www.navitassemi.com/.

- [47] B. Buono, R. Ghandi, M. Domeij, B. G. Malm, C. M. Zetterling and M. Ostling, "Modeling and characterization of current gain versus temperature in 4H-SiC power BJTs," in *IEEE Transactions on Electron Devices*, vol. 57, no. 3, pp. 704-711, Mar. 2010.

- [48] Y. Tian, R. Hedayati and C. M. Zetterling, "SiC BJT compact DC model with continuous- temperature scalability from 300 to 773 K," in *IEEE Transactions on Electron Devices*, vol. 64, no. 9, pp. 3588-3594, Sept. 2017.

H. Alan Mantooth received the B.S. (summa cum laude) and M. S. degrees in electrical engineering from the University of Arkansas in 1985 and 1986, respectively, and the Ph.D. degree from the Georgia Institute of Technology in 1990. He joined Analogy in 1990 where he focused on semiconductor device modeling and the research and development of HDL-based modeling tools and techniques. In 1998, he joined the faculty of the Department of Electrical Engineering at the

University of Arkansas, Fayetteville, where he currently holds the rank of Distinguished Professor. His research interests now involve analog and mixed-signal IC design & CAD, semiconductor device modeling, power electronics, and power electronic packaging. Dr. Mantooth helped establish the National Center for Reliable Electric Power Transmission (NCREPT) at the UA in 2005. Professor Mantooth serves as the Executive Director for NCREPT as well as two of its constitutive centers of excellence: the NSF I/ UCRC on GRid-connected Advanced Power Electronic Systems (GRAPES) and the DoE Cybersecurity Center on Secure, Evolvable Energy Delivery Systems (SEEDS). He also serves as the Deputy Director of the NSF ERC on Power Optimization of Electro-Thermal Systems (POETS). He currently holds the 21st Century Research Leadership Chair in the College of Engineering. Dr. Mantooth currently serves as President of the IEEE Power Electronics Society. He is a Fellow of IEEE, a member of Tau Beta Pi and Eta Kappa Nu, and registered professional engineer in Arkansas.

Tristan Evans Research Assistant at the University of Arkansas. Mr. Evans received his B.S. and M.S. degrees in electrical engineering from the University of Arkansas, Fayetteville in 2009 and 2011, respectively. Following that, he joined the R&D department of ROHM Semiconductor at their headquarters in Kyoto, Japan as an assistant researcher focusing on new die attach technology for SiC power devices and thermal modeling of SiC power modules. In the fall of 2016 he returned

to the University of Arkansas to pursue a Ph.D. in electrical engineering. His current research focuses on developing design automation tools for power electronics modules.

Chris Farnell NCREPT Interim Managing Director and Test Engineer. Mr. Farnell received his B.S. and M.S. degrees in electrical engineering from the University of Arkansas in 2010 and 2017, respectively. Prior to obtaining his degrees, Chris served in the United States Air Force as a Flying Crew Chief on the C-17A Globemaster III. His research interests include Embedded System Design, Wireless Networks, FPGAs, Cybersecurity, and Power Electronics. He is currently serving as the Interim

Managing Director and Test Engineer for the National Center for Reliable Electric Power Transmission (NCREPT) at the University of Arkansas. Chris remains active in K-12 outreach activities.

Quang Le received the B.S. (summa cum laude) degree in electrical engineering in December 2015 from the University of Arkansas, Fayetteville, AR, USA, where he is currently working towards the Ph.D. degree in electrical engineering. His current research focuses on automation design and optimization of power module.

Robert Murphree received the B.S. degree in electrical engineering in May 2015 from the University of Arkansas, Fayetteville, AR, USA, where he is currently working towards the master's degree in electrical engineering. His current research focuses on designing mixed-signal SiC integrated circuitry.