# A Survey on Space-Vector Pulse Width Modulation for Multilevel Inverters

Qamar Muhammad Attique, Yongdong Li, and Kui Wang

Abstract—The selection of an appropriate modulation scheme plays a vital role to assure the performance of multilevel inverters. Space vector pulse width modulation (SVPWM) is more efficient among all other pulse width modulation (PWM) techniques due to its key characteristics like better DC voltage utilization, switching losses reduction and easiness in digital implementation. The conventional SVPWM scheme presents some computational complexities due to redundant switching states and large number of space vectors. This paper summarizes five different SVPWM techniques for multilevel inverters which are  $\alpha$ - $\beta$  frame, g-h frame, K-L frame,  $\alpha'$ - $\beta'$  frame and SVPWM based on imaginary coordinate system. g-h frame and K-L frame are based on 60° and 120° coordinates system respectively. To compare the result of these SVPWM schemes, the complex calculations of conventional SVP-WM are converted into simplified line voltages form. The comparison results validate all the SVPWM techniques, but the SVPWM based on imaginary coordinate is found more simple in duty ratio calculations, easier to understand and provides a better control for zero-sequence component for any level of inverter.

Index Terms—g-h frame, imaginary coordinate system, K-L frame, multilevel inverters, space vector pulse width modulation (SVPWM),  $\alpha'$ - $\beta'$  frame.

# I. INTRODUCTION

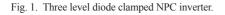

NowADAYS, the extensive use of multilevel inverters in high power and high voltage applications has made it a point of attraction for the researchers because of their remarkable performance. As compared with two-level inverters, multilevel inverters have various advantages, e.g. less harmonics in output current and voltages, reduced voltage stress across switching devices, lower dv/dt, better output wave form quality and lower common mode voltages [1], [2]. The diode-clamped 3 level neutral-point clamped (NPC) topology, as shown in Fig. 1 has been the most widely used one among all multilevel inverter topologies that have been proposed in literature [3]-[5].

By using an appropriate PWM technique, from discrete voltage levels, multilevel inverters generate the sinusoidal output voltages of different frequencies. Multilevel inverter's output performance depends on modulation algorithm and various PWM algorithms have been developed so far to fulfill the following objectives: less total harmonic distortion (THD), wider linear modulation range, lower switching losses and easy implementation. Among these, the two most popular PWM generation algorithms for multilevel inverters are sinusoidal carrier-based PWM (SPWM) and space vector PWM (SVPWM). In engineering applications, SPWM algorithms maintained their credibility for a long period [6]-[10] but with the development of microcontrollers, SVPWM took place due to its easy digital implementation, better harmonics performance, high DC voltage utilization ratio, reduced switching losses and convenience for capacitor voltage balancing. Moreover, the SVPWM has 15% higher linear modulation range than that of SPWM [11]. However, by increasing the number of levels, SVPWM faces the problem of more complex computations as compared to carrier-based PWM. Therefor many efforts have been made to achieve the SVPWM's performance by using zero-sequence voltage injection in carrier-based PWM [12]-[16]. Relationship between space vector and phase disposition carrier modulation is presented in [17] for hybrid and diode clamped multilevel inverters.

Any N-level inverter consists of six sectors and N<sup>3</sup> switching states in its space vector (SV) diagram while each sector comprises on (N-1)<sup>2</sup> triangles. There are  $1 + s \sum_{i=1}^{N-1} i$  (here S is the total number of sectors and N shows number of level) switching vectors having one or more switching states that depends on its location in space vector diagram. The switching states with equal line to line voltages are known as redundant states in SV diagram. By choosing an optimal switching sequence of these states, certain objectives can be accomplished such as: common-mode voltage reduction [18]-[20], extension of modulation index [21], fault tolerance operation [22], switching frequency reduction [20], [23] and balancing of DC link capacitor voltages [18], [24]-[27]. Voltage balancing of DC-link capacitors in NPC converters is one of the essential problems that causes the deviation of output voltages from the reference value, also damage the equipment and devices [28]-[33]. If the sinusoidal PWM algorithm is used, the control of neutral point voltage is done by injecting the appropriate zero-sequence voltage in the reference voltage [34]-[37]. A relation between zero-sequence voltage and neutral current for NPC three-level converters is presented in [38].

By increasing the level of inverter, number of switching states and triangles becomes quite large which causes complexities in on-time calculations of switching periods. For example, the space vector diagram for three-level inverter has 27 switching states and 24 triangles while five-level inverter has 125 switching states and 96 triangles. So, the traditional SVPWM algorithms [39], [40] by using trigonometric function calculations becomes impractical as level of inverters increases. So far, various SVPWM algorithms have been presented in literature [41]-

Manuscript received September 9, 2017.

The authors are with the Department of Electrical Engineering, Tsinghua University, Beijing 100084, China (e-mail: m\_atiq\_basra@yahoo.com; liyd@mail.tsinghua.edu.cn; wangkui@mail.tsinghua.edu.cn).

Digital Object Identifier 10.24295/CPSSTPEA.2017.00021

[51] to diminish the problem of computational complexities.

A decomposition method was introduced in [41] and also implemented in [42], [43], by which the SV hexagon of three-level inverter is decomposed into six two-level SV hexagons. This method still has huge complications for increased level. For five-level inverter, SV diagram should be decomposed into six hexagons of four-level and then each four-level hexagon should be decomposed into six hexagons of three-level and so on. A fast SVPWM algorithm based on 60° coordinate system has been presented in [44] but does not consider proper switching states sequence and capacitor voltage balancing. Another effort has been made in [47] by proposing a general SVPWM algorithm based on imaginary coordinate system including the control of zero-sequence component. Two different non-orthogonal SVPWM strategies have been implemented in [48] and [51].

This paper summarizes the five different SVPWM algorithms for multilevel inverters which are  $\alpha$ - $\beta$  frame, g-h frame, K-Lframe,  $\alpha'$ - $\beta'$  frame and SVPWM based on imaginary coordinate system. The complex calculations of conventional SVPWM are converted into simplified line voltages form and the results are compared for all aforementioned algorithms. The comparison results validate all the SVPWM techniques, but the SVPWM based on imaginary coordinate is more simple in duty ratio calculations, easier to understand and provides a better control for zero-sequence component for any level of inverter.

# II. THE CONVENTIONAL ( $\alpha$ - $\beta$ Frame) SVPWM Algorithm

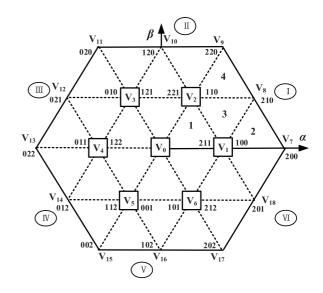

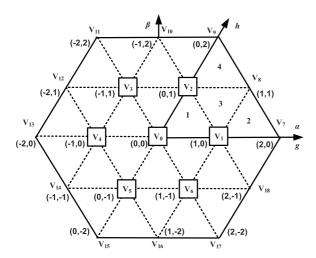

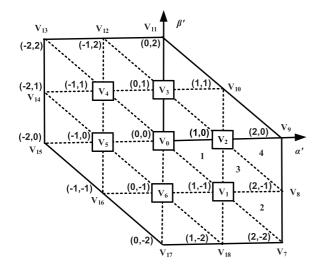

The basic diagram of 3-level diode-clamped inverter is shown in Fig. 1 which contains twelve switching devices (four in each leg) and three output levels for each phase (2, 1, 0). The relation between these devices and output level of each leg is shown in TABLE I. Fig. 2 shows the space vector diagram of three level inverter which consists of 24 active voltage vectors (6 large vectors, 6 medium vectors, 12 small vectors) and three zero vectors (222, 111, 000). SV diagram is divided in to six sectors (labeled as sector I to VI), each sector is divided into four triangles (labeled as triangle 1 to 4), 24 triangles in total. The implementation of space vector PWM comprises of the sector identification where the reference voltage vector is located, identification of three nearest switching vectors, selection of an appropriate switching sequence and on-time calculation of switches for specific switching sequence.

The reference vector  $V_{\rm ref}$  corresponding to the three-phase

TABLE I Relationship Between Switching Devices and Output Level

| ON Devices                        | OFF Devices                       | Output Level | Terminal Voltage    |

|-----------------------------------|-----------------------------------|--------------|---------------------|

| S <sub>x1</sub> , S <sub>x2</sub> | S <sub>x3</sub> , S <sub>x4</sub> | 2            | $+V_{dc}/2$         |

| S <sub>x2</sub> , S <sub>x3</sub> | $S_{x1}, S_{x4}$                  | 1            | 0                   |

| S <sub>x3</sub> , S <sub>x4</sub> | $S_{x1}, S_{x2}$                  | 0            | -V <sub>dc</sub> /2 |

Fig. 2. Space vector diagram of three level NPC inverter.

voltages is defined by

$$V_{ref} = 2 \left( V_a + V_{b} e^{j2\pi/3} + V_{c} e^{-j2\pi/3} \right) / 3.$$

(1)

By using Clark transformation, three-phase coordinate system *a-b-c* is transformed to 2-dimentional  $\alpha$ - $\beta$  frame which is helpful in sector identification by following expression:

$$\begin{bmatrix} V_{r\alpha} \\ V_{r\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \sqrt{3} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_{\alpha} \\ V_{b} \\ V_{c} \end{bmatrix}$$

(2)

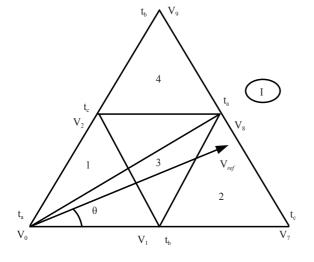

where  $V_{r\alpha}$  and  $V_{r\beta}$  are the components of reference vector in  $\alpha$ - $\beta$  coordinate system. The reference voltage vector can be located in any region (1-4) of any sector (I-VI) in space vector diagram as shown in Fig. 2. For example, considering that the reference vector  $V_{ref}$  is locating in region 2 of sector I, the nearest three voltage vectors for this region are  $V_1$ ,  $V_7$  and  $V_8$  are shown in Fig. 3.

After identification of nearest three vectors, the following expressions can be developed for the on-time calculations of the corresponding vectors by using the volt-second balance method

$$V_{ref}T_{s} = V_{8ta} + V_{1tb} + V_{7tc} T_{s} = t_{a} + t_{b} + t_{c}$$

(3)

where  $T_s$  is the sampling time,  $t_a$ ,  $t_b$  and  $t_c$  are the on-times for

=

Fig. 3. Vector representation in sector I.

the voltage vectors  $V_8$ ,  $V_1$  and  $V_7$  respectively. By solving (3), the on-time of the corresponding vectors can be computed by

$$t_{a} = a \sin \theta / \sqrt{3}$$

$$t_{b} = 2T_{s} - a \sin (\theta + \pi/3) / \sqrt{3}$$

$$t_{c} = -T_{s} - a \sin (\theta - \pi/3) / \sqrt{3}$$

(4)

where  $a=3T_s$  ( $V_{ref}/V_{dc}$ ). The on-times for all the corresponding vectors in remaining regions of sector I can be computed by using similar procedure as expressed in TABLE II.

TABLE II On-Times in Sector I

|          | t <sub>a</sub>                           | $t_b$                                             | t <sub>c</sub>                                    |

|----------|------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| Region 1 | $T_s - a \sin(\theta + \pi/3)/\sqrt{3}$  | $-a\sin(\theta - \pi/3)/\sqrt{3}$                 | $a\sin\theta/\sqrt{3}$                            |

| Region 2 | $a\sin\theta/\sqrt{3}$                   | $\frac{2T_s - a\sin{(\theta + \pi/3)}}{\sqrt{3}}$ | $-T_s - a \sin(\theta - \pi/3)/\sqrt{3}$          |

| Region 3 | $-T_s + a \sin(\theta + \pi/3)/\sqrt{3}$ | $T_s - a \sin\theta / \sqrt{3}$                   | $T_s + a \sin(\theta - \pi/3)/\sqrt{3}$           |

| Region 4 | $-a\sin(\theta - \pi/3)/\sqrt{3}$        | $-T_s + a \sin\theta / \sqrt{3}$                  | $\frac{2T_s - a\sin{(\theta + \pi/3)}}{\sqrt{3}}$ |

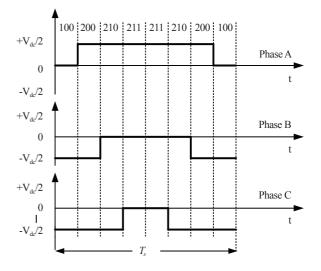

The next step in implementation of SVPWM is the selection of optimal switching sequence of the redundant states which is helpful in balancing of DC link capacitor voltages, fault tolerance and switching frequency reduction etc. TABLE III shows all possible switching sequence for all regions of sector I and Fig. 4 is the graphical representation for region 2.

The conventional SVPWM requires a huge amount of trigonometric operations to calculate the on-times of the switches which needs more storage space and additional hardware. There are three types of trigonometric functions ( $\sin\theta$ ,  $\sin(\theta+\pi/3)$ ,  $\sin(\theta-\pi/3)$ ) in TABLE I. These trigonometric functions can be

TABLE III POSSIBLE SWTTCHING SEQUENCE FOR SECTOR I

| Region | Switching Sequence                                                                           |

|--------|----------------------------------------------------------------------------------------------|

| 1      | (i) 222-221-211-111<br>(ii) 000-100-110-111<br>(iii) 221-211-111-110<br>(iv) 211-111-110-100 |

| 2      | (i) 221-211-210-110<br>(ii) 211-210-110-100                                                  |

| 3      | 221-220-210-110                                                                              |

| 4      | 211-210-200-100                                                                              |

Fig. 4. Switching sequence for region 2.

converted into simplified line voltages form by using few calculations as follows:

$$\left| V_{ref} \right| \sin \theta = \left| V_{ref} \right| \sqrt{\tan^2 \theta / (1 + \tan^2 \theta)}$$

(5)

$$\left|V_{ref}\right| = \sqrt{\frac{2}{3} \left[ \left(V_a - \frac{1}{2}V_b - \frac{1}{2}V_c\right)^2 + \left(\frac{\sqrt{3}}{2}V_b - \frac{\sqrt{3}}{2}V_c\right)^2 \right]} \quad (6)$$

$$\tan \theta = \frac{\operatorname{Re}(V_{ref})}{\operatorname{Im}(V_{ref})} = \frac{\frac{\sqrt{3}2 V_b - \sqrt{3}2 V_c}{V_a - \frac{1}2 V_b - \frac{1}2 V_c}$$

(7)

By using (6) and (7) into (5), the result in simplified line voltages form is

$$\left| V_{ref} \right| \sin \theta = V_{bc} / \sqrt{3} \tag{8}$$

The remaining two trigonometric functions can be calculated by using same method and the results are shown in (9) and (10).

$$V_{ref} \left| \sin \left( \theta + \pi/3 \right) = -V_{ca} / \sqrt{3} \right|$$

(9)

$$\left|V_{ref}\right|\sin\left(\theta - \pi/3\right) = -V_{ab}/\sqrt{3} \tag{10}$$

Now the complex computations of the conventional SVP-WM algorithm are converted into simplified line voltages form by replacing the values of trigonometric functions as shown in TABLE IV.

| ON-TIMES IN LINE VOLTAGES FORM FOR SECTOR I |                                              |                                             |                                             |  |  |

|---------------------------------------------|----------------------------------------------|---------------------------------------------|---------------------------------------------|--|--|

|                                             | $t_a$                                        | $t_b$                                       | $t_c$                                       |  |  |

| Region 1                                    | $T_s\left(1+\frac{V_{ca}}{V_{dc}}\right)$    | $T_s \frac{V_{ab}}{V_{dc}}$                 | $T_s \frac{V_{bc}}{V_{dc}}$                 |  |  |

| Region 2                                    | $T_s rac{V_{bc}}{V_{dc}}$                   | $T_s\left(2 + \frac{V_{ca}}{V_{dc}}\right)$ | $T_s\left(-1+\frac{V_{ab}}{V_{dc}}\right)$  |  |  |

| Region 3                                    | $T_{s}\left(-1-\frac{V_{ca}}{V_{dc}}\right)$ | $T_s\left(1-\frac{V_{bc}}{V_{dc}}\right)$   | $T_s\left(1-\frac{V_{ab}}{V_{dc}}\right)$   |  |  |

| Region 4                                    | $T_s rac{V_{ab}}{V_{dc}}$                   | $T_s\left(-1+\frac{V_{bc}}{V_{dc}}\right)$  | $T_s\left(2 + \frac{V_{ca}}{V_{dc}}\right)$ |  |  |

TABLE IV ON-TIMES IN LINE VOLTAGES FORM FOR SECTOR I

# III. SVPWM BASED ON g-h COORDINATE SYSTEM

The space vector diagram for three-level inverter based on  $60^{\circ}$  coordinate system is shown in Fig. 5. The *g*-axis overlapped with  $\alpha$ -axis and the *h*-axis is  $60^{\circ}$  apart from *g*-axis in counter-clockwise direction.

Fig. 5. Space vector diagram of inverter in g-h frame.

# A. Coordinate Transformation

The transformation of reference vector  $V_{ref}$  from three-phase system to two dimensional *g*-*h* frame is the basic step of this algorithm. The relation between  $\alpha$ - $\beta$  coordinate system and *g*-*h* coordinate system is given by

$$\begin{bmatrix} V_{r\alpha} \\ V_{r\beta} \end{bmatrix} = \begin{bmatrix} 1 & \frac{1}{2} \\ 0 & \sqrt{3} \\ 2 \end{bmatrix} \begin{bmatrix} V_{rg} \\ V_{rh} \end{bmatrix}$$

(11)

$$\begin{bmatrix} V_{rg} \\ V_{rh} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{\sqrt{3}} \\ 0 & \frac{2}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} V_{r\alpha} \\ V_{r\beta} \end{bmatrix}$$

(12)

where  $V_{\rm rg}$  and  $V_{\rm rh}$  are the components of reference voltage vector  $V_{\rm ref}$  in *g*-*h* coordinate system. By using (2) and (12) the desired coordinate transformation can be achieved as shown in the following expression.

$$\begin{bmatrix} V_{rg} \\ V_{rh} \end{bmatrix} = \begin{bmatrix} 1 & -1 & 0 \\ 0 & 1 & -1 \end{bmatrix} \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$$

(13)

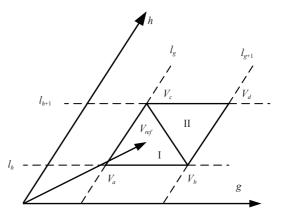

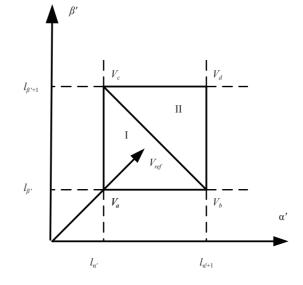

Fig. 6 shows that the lines  $l_g$ ,  $l_g+1$ ,  $l_g+2$ .... are parallel to the *h*-axis and the projections of every vector located on these lines are  $gV_{dc}$ ,  $(g+1) V_{dc}$ ,  $(g+2) V_{dc}$ .... respectively on the *g*-axis. Similarly the lines  $l_h$ ,  $l_h+1$ ,  $l_h+2$ .... are parallel to the *g*-axis and the projections of every vector located on these lines are  $hV_{dc}$ ,  $(h+1) V_{dc}$ ,  $(h+2) V_{dc}$ .... respectively on the *h*-axis.

# B. Identification of Nearest Three Vectors

All the switching vectors in *g*-*h* coordinate system have only integer coordinates, so the real values of the coordinates are rounded down to the integer values by using the *int*() function.

$$g = int(V_{rg}) h = int(V_{rh})$$

(14)

The nearest four vectors constitute a rhombus which is divided into triangle I and triangle II as shown in Fig. 6. The coordinates of vectors  $V_a$ ,  $V_b$ ,  $V_c$  and  $V_d$  are (*int* ( $V_{rg}$ ), *int* ( $V_{rh}$ )), (*int* ( $V_{rg}$ )+1, *int* ( $V_{rh}$ )), (*int* ( $V_{rg}$ ), *int* ( $V_{rh}$ )+1), and (*int* ( $V_{rg}$ )+1, *int* ( $V_{rh}$ )+1) respectively. The reference vector is locating in triangle I or triangle II, the decision can be made by the following expression:

$$V_{ca}+1 \ge -(g+h) \qquad V_{ref} \text{ in triangle I} V_{ca}+1 \le -(g+h) \qquad V_{ref} \text{ in triangle I}$$

(15)

Fig. 6. The composition of space vector in g-h frame.

229

and

# C. Duty Cycle Calculation

Assuming that the reference vector is locating in triangle I, the nearest three vectors are  $V_a$ ,  $V_b$  and  $V_c$ . The duty ratio of the corresponding vectors can be calculated by

$$\left. \begin{array}{c} V_{ref}T_s = V_{a}t_a + V_{b}t_b + V_{c}t_c \\ T_s = t_a + t_b + t_c \end{array} \right\}.$$

$$(16)$$

Transforming (16) into g-h coordinates yields

$$V_{rg}T_{s} = V_{agt}g_{,h} + V_{bgt}g_{+1,h} + V_{cgt}g_{,h+1} V_{rh}T_{s} = V_{ah}t_{g,h} + V_{bh}t_{g+1,h} + V_{ch}t_{g,h+1} T_{s} = t_{g,h} + t_{g+1,h} + t_{g,h+1}$$

(17)

By solving (17), the on-time of the corresponding vectors can be computed by

$$t_{g,h} = T_s \left( (V_{ca}/V_{dc}) + g + h + 1 \right) t_{g+1,h} = T_s \left( (V_{ab}/V_{dc}) - g \right) t_{g,h+1} = T_s \left( (V_{bc}/V_{dc}) - h \right)$$

(18)

Similarly, when the reference vector is locating in triangle II, the on-times for the vectors  $V_b$ ,  $V_c$  and  $V_d$  can be calculated by

$$t_{g+1,h} = T_s \left( -(V_{bc}/V_{dc}) + g + 1) \\ t_{g,h+1} = T_s \left( -(V_{ab}/V_{dc}) + g + 1) \\ t_{g+1,h+1} = T_s \left( -(V_{ca}/V_{dc}) - g - h - 1) \right) \right\}.$$

(19)

Assuming that, the amplitude of reference vector is  $1.386V_{dc}$ and it is 25° electrical with respect to the *a*-axis. The corresponding line voltages are

$$\begin{bmatrix} V_{ab} \\ V_{bc} \\ V_{ca} \end{bmatrix} = 1.386 \cdot V_{dc} \begin{bmatrix} 0.574 \\ 0.422 \\ -0.966 \end{bmatrix}$$

(20)

and the value of  $V_{rg}$  and  $V_{rh}$  is  $0.795V_{dc}$  and  $0.585V_{dc}$  respectively. The exact location of reference vector can be determined by using (15).

$$V_{ca} + 1 \le -(g+h) = -0.380 < 0 \tag{21}$$

The reference vector is located in triangle 3 in Fig. 5 and the nearest three vectors are  $V_1(1, 0)$ ,  $V_2(0, 1)$  and  $V_8(1, 1)$ . The duty cycle for these vectors is calculated by (19).

$$\begin{array}{c} t_1 = 0.415T_s \\ t_2 = 0.205T_s \\ t_8 = 0.380T_s \end{array}$$

(22)

# D. Switching-State Selection

The last step of the algorithm is to transform the two-dimen-

sional system back to three-dimensional switching states by using the following expression:

$$\begin{bmatrix} S_A \\ S_B \\ S_C \end{bmatrix} = \begin{bmatrix} i \\ i-g \\ i-h \end{bmatrix} \in (0,1,2), \quad i \in (0,1,2)$$

(23)

For example, the vectors (0, 1) and (1, 1) in the Fig. 5 can be transformed into  $(1 \ 1 \ 0)$ ,  $(2 \ 2 \ 1)$  and  $(2 \ 1 \ 0)$  switching states respectively.

# IV. SVPWM BASED ON K-L COORDINATE SYSTEM

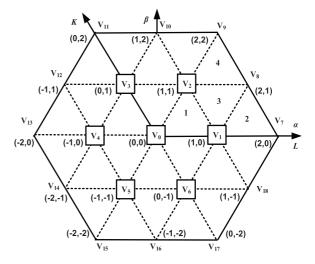

The *K*-*L* coordinate system is also called 120° coordinate system. Fig. 7 shows the space vector diagram for three-level inverter based on *K*-*L* coordinate system. The *L*-axis coincided with  $\alpha$ -axis and the *K*-axis is 120° apart from *L*-axis in counter-clockwise direction.

Fig. 7. Space vector diagram of inverter in K-L frame.

# A. Coordinate Transformation

The initial step that is required in this algorithm is the transformation of reference vector  $V_{ref}$  from three-dimensional system to two dimensional *K-L* coordinate system. The relation between  $\alpha$ - $\beta$  coordinate system and *K-L* coordinate system is given by

$$\begin{bmatrix} V_{r\alpha} \\ V_{r\beta} \end{bmatrix} = \begin{bmatrix} 1 & -\frac{1}{2} \\ 0 & \sqrt{3}/2 \end{bmatrix} \begin{bmatrix} V_{rL} \\ V_{rK} \end{bmatrix}$$

(24)

and

$$\begin{bmatrix} V_{rL} \\ V_{rK} \end{bmatrix} = \begin{bmatrix} 1 & \frac{1}{\sqrt{3}} \\ 0 & \frac{2}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} V_{r\alpha} \\ V_{r\beta} \end{bmatrix}$$

(25)

where  $V_{\rm rL}$  and  $V_{\rm rK}$  are the components of reference voltage vec-

tor  $V_{\text{ref}}$  in *K-L* coordinate system while  $V_{\text{re}}$  and  $V_{\text{r}\beta}$  are the components of  $V_{\text{ref}}$  in  $\alpha$ - $\beta$  coordinate system. By using (2) and (25) the desired coordinate transformation can be achieved as shown in the following expression:

$$\begin{bmatrix} V_{rL} \\ V_{rK} \end{bmatrix} = \begin{bmatrix} 1 & 0 & -1 \\ 0 & 1 & -1 \end{bmatrix} \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}.$$

(26)

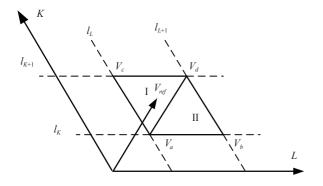

The lines  $l_L$ ,  $l_L+1$ ,  $l_L+2$ .... are parallel to the *K*-axis and the components of every vector located on these lines are  $LV_{dc}$ , (L+1)  $V_{dc}$ , (L+2)  $V_{dc}$ .... respectively on the *L*-axis as shown in Fig. 8. Similarly the lines  $l_K$ ,  $l_K+1$ ,  $l_K+2$ .... are parallel to the *L*-axis and the components of every vector located on these lines are  $KV_{dc}$ , (K+1)  $V_{dc}$ , (K+2)  $V_{dc}$ ..... respectively on the *K*-axis.

Fig. 8. The composition of space vector in K-L frame.

# B. Identification of Nearest Three Vectors

As shown in Fig. 7, all the switching vectors in *K*-*L* coordinate system have only integer coordinates, so the real values of the coordinates are rounded down to the integer values by using the *int*() function.

$$L = \operatorname{int}(V_{rL}) K = \operatorname{int}(V_{rK})$$

(27)

The coordinates of the nearest four vectors  $V_a$ ,  $V_b$ ,  $V_c$  and  $V_d$  are (*int* ( $V_{rL}$ ), *int* ( $V_{rK}$ )), (*int* ( $V_{rL}$ )+1, *int* ( $V_{rK}$ )), (*int* ( $V_{rL}$ ), *int* ( $V_{rK}$ )+1) and (*int* ( $V_{rL}$ )+1, *int* ( $V_{rK}$ )+1) respectively. Whether the reference vector is locating in triangle I or triangle II, the decision can be made by the following expression:

$$V_{ab} \le L - K \qquad V_{ref} \text{ in triangle I} V_{ab} \ge L - K \qquad V_{ref} \text{ in triangle II}$$

(28)

# C. Duty Cycle Calculation

Assuming that the reference vector is locating in triangle I, the nearest three vectors are  $V_a$ ,  $V_c$  and  $V_d$ . The duty ratio of the corresponding vectors can be calculated by

$$\left. \begin{array}{c} V_{ref}T_s = V_{ata} + V_{ctc} + V_{dtd} \\ T_s = t_a + t_c + t_d \end{array} \right\}.$$

(29)

Transforming (29) into K-L coordinates yields

$$V_{rL}T_{s} = V_{aL}t_{L,K} + V_{cL}t_{L,K+1} + V_{dL}t_{L+1,K+1} V_{rh}T_{s} = V_{aK}t_{L,K} + V_{cK}t_{L,K+1} + V_{dK}t_{L+1,K+1} T_{s} = t_{L,K} + t_{L,K+1} + t_{L+1,K+1}$$

(30)

By solving (30), the on-time of the corresponding vectors can be computed by

$$\left. \begin{array}{l} t_{L,K} = T_s \left( -(V_{bc}/V_{dc}) + K + 1 \right) \\ t_{L,K+1} = T_s \left( -(V_{ab}/V_{dc}) + L - K \right) \\ t_{L+1,K+1} = T_s \left( -(V_{ca}/V_{dc}) - L \right) \end{array} \right\}.$$

(31)

Similarly, when the reference vector is locating in triangle II, the on-times for the vectors  $V_a$ ,  $V_b$  and  $V_d$  can be calculated by

$$\left. \begin{array}{c} t_{L,K} = T_{s} \left( (V_{ca}/V_{dc}) + L + 1 \right) \\ t_{L+1,K} = T_{s} \left( (V_{ab}/V_{dc}) - L + K \right) \\ t_{L+1,K+1} = T_{s} \left( (V_{bc}/V_{dc}) - K \right) \end{array} \right\}.$$

(32)

For example, by keeping the amplitude and angle of the reference vector same as *g*-*h* coordinate system, the value of  $V_{\rm rL}$ and  $V_{\rm rK}$  is  $1.380V_{dc}$  and  $0.585V_{dc}$  respectively. The exact location of reference vector can be determined by using (28).

$$V_{ab} \le L - K = 0.795 < 1 \tag{33}$$

The reference vector is located in triangle 3 in Fig. 7 and the nearest three vectors are  $V_1(1, 0)$ ,  $V_2(0, 1)$  and  $V_8(1, 1)$ . The duty cycle for these vectors is calculated by (31).

$$\begin{array}{c} t_1 = 0.415T_s \\ t_2 = 0.205T_s \\ t_8 = 0.380T_s \end{array}$$

(34)

# D. Switching-State Selection

The last step of the algorithm is to transform the two-dimensional system back to three-dimensional switching states by using the following expression.

$$\begin{bmatrix} S_A \\ S_B \\ S_C \end{bmatrix} = \begin{bmatrix} i+L \\ i+K \\ i \end{bmatrix} \in (0,1,2), \quad i \in (0,1,2)$$

(35)

For example, the vectors (1, 0) and (2, 0) in the Fig. 7 can be transformed into  $(1 \ 0 \ 0)$ ,  $(2 \ 1 \ 1)$  and  $(2 \ 0 \ 0)$  switching states

231

respectively.

# V. SVPWM Based on $\alpha' - \beta'$ Coordinate System

The conventional SVPWM algorithm is based on  $\alpha$ - $\beta$  coordinate system and reference vector rotates in a circular trajectory. In this algorithm, circular trajectory of reference vector is transformed into an elliptical trajectory in  $\alpha'$ - $\beta'$  frame as shown in Fig. 9.

# A. Coordinate Transformation

The relationship between  $\alpha$ - $\beta$  frame and  $\alpha'$ - $\beta'$  frame is given by

$$\begin{bmatrix} V_{r\alpha} \\ V_{r\beta} \end{bmatrix} = \begin{bmatrix} \frac{1}{2} & -\frac{1}{2} \\ \sqrt{3}/2 & \sqrt{3}/2 \end{bmatrix} \begin{bmatrix} V_{r\alpha'} \\ V_{r\beta'} \end{bmatrix}$$

(36)

and

$$\begin{bmatrix} V_{r\alpha'} \\ V_{r\beta'} \end{bmatrix} = \begin{bmatrix} 1 & \frac{1}{\sqrt{3}} \\ -1 & \frac{1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} V_{r\alpha} \\ V_{r\beta} \end{bmatrix}$$

(37)

where  $V_{\rm rc'}$  and  $V_{\rm r\beta'}$  are the components of reference voltage vector  $V_{\rm ref}$  in  $\alpha'$ - $\beta'$  coordinate system. The coordinate transformation from three-phase system to  $\alpha'$ - $\beta'$  frame can be achieved by using (2) and (37) as shown in (38).

$$\begin{bmatrix} V_{r\alpha'} \\ V_{r\beta'} \end{bmatrix} = \begin{bmatrix} 1 & 0 & -1 \\ -1 & 1 & 0 \end{bmatrix} \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$$

(38)

Fig. 9. Space vector diagram of inverter in  $\alpha'$ - $\beta'$  frame.

# B. Identification of Nearest Three Vectors

As shown in Fig. 10, the vertices of the vectors  $V_a$ ,  $V_b$  and  $V_c$

constitute triangles I and triangle II is made by the vertices of the vectors  $V_b$ ,  $V_c$  and  $V_d$ . The coordinates of the nearest four vectors  $V_a$ ,  $V_b$ ,  $V_c$  and  $V_d$  are (*int* ( $V_{r\alpha}$ ), *int* ( $V_{r\beta}$ )), (*int* ( $V_{r\alpha}$ )+1, *int* ( $V_{r\beta}$ )), (*int* ( $V_{r\alpha}$ ), *int* ( $V_{r\beta}$ )+1) and (*int* ( $V_{r\alpha}$ )+1, *int* ( $V_{r\beta}$ )+1) respectively. *int*() is a function that is used to round down the real values to the integer values of the coordinates.

$$\begin{array}{l} \alpha' = \operatorname{int}(V_{r\alpha'}) \\ \beta' = \operatorname{int}(V_{r\beta'}) \end{array}$$

$$(39)$$

Fig. 10. The composition of space vector in  $\alpha'$ - $\beta'$  frame.

Vectors  $V_b$  and  $V_c$  are always the nearest two vectors while the third nearest vector will be decided by the following expression:

$$W = V_{bc} - \alpha' - \beta' - 1.$$

(40)

If W < 0, the third nearest vector will be  $V_a$  and  $V_{ref}$  will be located in triangle I; otherwise, reference vector will be in triangle II.

# C. Duty Cycle Calculation

Assuming that the reference vector is locating in triangle I, the nearest three vectors are  $V_a$ ,  $V_b$  and  $V_c$ . The duty ratio of the corresponding vectors can be calculated by

$$\left. \begin{array}{c} V_{ref}T_s = V_at_a + V_bt_b + V_ct_c \\ T_s = t_a + t_b + t_c \end{array} \right\}.$$

$$(41)$$

Transforming (41) into  $\alpha' - \beta'$  coordinates yields

$$V_{r\alpha'}T_s = V_{a\alpha'}t_{\alpha',\beta'} + V_{b\alpha'}t_{\alpha'+1,\beta'} + V_{c\alpha'}t_{\alpha',\beta'+1} V_{r\beta'}T_s = V_{a\beta'}t_{\alpha',\beta'} + V_{b\beta'}t_{\alpha'+1,\beta'} + V_{c\beta'}t_{\alpha',\beta'+1} T_s = t_{\alpha',\beta'} + t_{\alpha'+1,\beta'} + t_{\alpha',\beta'+1}$$

$$(42)$$

By solving (42), the on-time of the corresponding vectors can

be computed by

$$t_{\alpha',\beta'} = T_s \left( -(V_{bc}/V_{dc}) + \alpha' + \beta' + 1) \right) t_{\alpha'+1,\beta'} = T_s \left( -(V_{ca}/V_{dc}) - \alpha') \right) t_{\alpha',\beta'+1} = T_s \left( -(V_{ab}/V_{dc}) - \beta') \right) .$$

(43)

Similarly, when the reference vector is locating in triangle II, the on-times for the vectors  $V_b$ ,  $V_c$  and  $V_d$  can be calculated by

$$\begin{aligned} & t_{\alpha'+1,\beta'} = T_s \left( (V_{ab}/V_{dc}) + \beta' + 1 \right) \\ & t_{\alpha',\beta'+1} = T_s \left( (V_{ca}/V_{dc}) + \alpha' + 1 \right) \\ & t_{\alpha'+1,\beta'+1} = T_s \left( (V_{bc}/V_{dc}) - \alpha' - \beta' - 1 \right) \end{aligned}$$

(44)

As an example, consider that the amplitude of reference vector is  $1.386V_{dc}$  and the angle is 25° same as used in previous algorithms. So, the line voltages remain same and the value of  $V_{rat}$  and  $V_{rg}$  is given by

$$\begin{bmatrix} V_{r\alpha'} \\ V_{r\beta'} \end{bmatrix} = V_{dc} \begin{bmatrix} 1.380 \\ -0.795 \end{bmatrix}.$$

(45)

The exact location of reference vector can be determined by the sign of (40).

$$W = V_{bc} - \alpha' - \beta' - 1 = 0.585 - 1 + 1 - 1 = -0.415$$

(46)

The sign of the above expression is negative so the reference vector is located in triangle 3 in Fig. 9 and the nearest three vectors are  $V_1(1, -1)$ ,  $V_2(1, 0)$  and  $V_8(2, -1)$ . The duty cycle for these vectors is calculated by (43).

$$\begin{array}{c} t_1 = 0.415T_s \\ t_2 = 0.205T_s \\ t_8 = 0.380T_s \end{array}$$

(47)

#### D. Switching-State Selection

The last step of the algorithm is to transform the two-dimensional system back to three-dimensional switching states by using the following expression:

$$\begin{bmatrix} S_A \\ S_B \\ S_C \end{bmatrix} = \begin{bmatrix} i \\ i+\beta' \\ i-\alpha' \end{bmatrix} \in (0,1,2), \quad i \in (0,1,2).$$

(48)

For example, the vectors (0, -1) and (-1, 2) in the Fig. 9 can be transformed into  $(1 \ 0 \ 1)$ ,  $(2 \ 1 \ 2)$  and  $(0 \ 2 \ 1)$  switching states respectively.

# VI. SVPWM BASED ON IMAGINARY COORDINATE SYSTEM

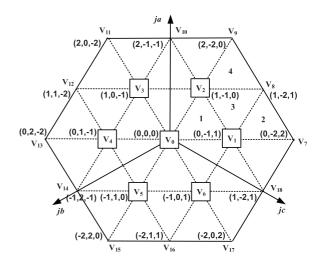

The space vector diagram for three-level inverter based on imaginary coordinate system is shown in Fig. 11. Three axis of imaginary coordinate system ja, jb and jc are perpendicular to the three-phase axis a, b and c respectively [52].

Fig. 11. Space vector diagram of inverter in *ja-jb-jc* frame.

#### A. Coordinate Transformation

The transformation from phase coordinate to the imaginary coordinate is given by

$$\begin{bmatrix} V_{ja} \\ V_{jb} \\ V_{jc} \end{bmatrix} = \begin{bmatrix} 0 & 1 & -1 \\ -1 & 0 & 1 \\ 1 & -1 & 0 \end{bmatrix} \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$$

(49)

where  $V_{ja}$ ,  $V_{jb}$ ,  $V_{jc}$  are variables of imaginary coordinate system and  $V_a$ ,  $V_b$ ,  $V_c$  are variables in phase coordinate system. The relation between imaginary frame and  $\alpha$ - $\beta$  frame is given by

$$\begin{bmatrix} V_{ja} \\ V_{jb} \\ V_{jc} \end{bmatrix} = \begin{bmatrix} 0 & \sqrt{2} \\ -\sqrt{3/2} & -\frac{1}{\sqrt{2}} \\ \sqrt{3/2} & -\frac{1}{\sqrt{2}} \end{bmatrix} \begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix}.$$

(50)

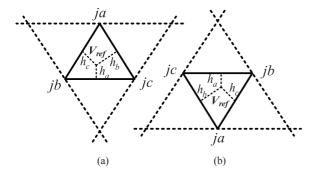

# B. Identification of Nearest Three Vectors

All the vectors in imaginary coordinate system have integer values as shown in Fig. 11. *int*() is a function that is used to rounded down the real values to the integer values:  $V_{ja}=int (V_{rja})$ ,  $V_{jb}=int (V_{rjb})$ ,  $V_{jc}=int (V_{rjc})$ . There are two possible directions of equilateral triangles as shown in Fig. 12. If *int*  $(V_{rja})+int (V_{rjb})+int (V_{rjc})=-1$ , then the reference vector is locating in normal direction triangle and if *int*  $(V_{rja})+int (V_{rjb})+int (V_{rjc})=-2$ , then the reference vector is locating in.

## C. Duty Cycle Calculation

Assuming that the reference vector is locating in normal direction triangle. The coordinates of three vertices are  $(V_{ia}+1, V_{ib})$   $V_{jc}$ -1),  $(V_{ja}, V_{jb}$ +1,  $V_{jc}$ -1) and  $(V_{ja}, V_{jb}, V_{jc})$ . The time duration for these vertices is calculated by

$$V_{ref} = V_{jad} _{ja} + V_{jbd} _{jb} + V_{jc} d_{jc} d_{ja} + d_{jb} + d_{jc} = 1$$

(51)

where  $d_{ja}=h_a$ ,  $d_{jb}=h_b$  and  $d_{jc}=h_c$  are the duty ratio for the vertices and  $T_s$  is the sampling time.  $h_a$ ,  $h_b$  and  $h_c$  represents the distance from the edges of triangle to the reference vector and computed by

$$\begin{array}{l} h_{a} = V_{rja} - \operatorname{int}(V_{rja}) \\ h_{b} = V_{rjb} - \operatorname{int}(V_{rjb}) \\ h_{c} = V_{rjc} - \operatorname{int}(V_{rjc}) \end{array} \right\} .$$

$$(52)$$

Fig. 12. Two possible directions of triangle. (a) normal direction and (b) reverse direction.

By using (51) and (52), the duty ratio for the corresponding vertices in line voltages form can be obtained by

$$t_{ja} = T_{s} \left( (V_{bc}/V_{dc}) - V_{ja} \right)$$

$$t_{jb} = T_{s} \left( (V_{ca}/V_{dc}) - V_{jb} \right)$$

$$t_{jc} = T_{s} \left( (V_{ab}/V_{dc}) - V_{jc} \right)$$

(53)

Similarly, when the reference vector is locating in reverse direction triangle, the duty ratio for the corresponding vertices is calculated by

$$t_{ja} = T_{S} \left( -(V_{bc}/V_{dc}) + V_{ja} + 1) \right)$$

$$t_{jb} = T_{S} \left( -(V_{ca}/V_{dc}) + V_{jb} + 1) \right)$$

$$t_{ic} = T_{S} \left( -(V_{ab}/V_{dc}) + V_{ic} + 1) \right)$$

$$(54)$$

For example, considering that the length and the angle of reference vector is  $1.386V_{dc}$  and  $25^{\circ}$  respectively. The line voltages are given by

$$\begin{bmatrix} V_{ja} \\ V_{jb} \\ V_{jc} \end{bmatrix} = \begin{bmatrix} V_{bc} \\ V_{ca} \\ V_{ab} \end{bmatrix} = V_{dc} \begin{bmatrix} 0.585 \\ -1.380 \\ 0.795 \end{bmatrix}.$$

(55)

The exact location of reference vector, whether it is located in

normal direction triangle or in reverse direction triangle is determined by the following expression:

$$\operatorname{int}(V_{rja}) + \operatorname{int}(V_{rjb}) + \operatorname{int}(V_{rjc}) = 0 - 2 + 0 = -2.$$

(56)

Because the value is -2, so the reference vector is located in reverse direction triangle and the nearest three vectors are  $V_1(0, -1, 1)$ ,  $V_2(1, -1, 0)$  and  $V_8(1, -2, 1)$ . The duty cycle for these vectors is calculated by (54).

$$\begin{array}{c} t_{ja} = t_1 = 0.415T_s \\ t_{jc} = t_2 = 0.205T_s \\ t_{jb} = t_s = 0.380T_s \end{array}$$

(57)

# D. Switching-State Selection

The last step of the algorithm is to transform the two-dimensional system back to three-dimensional switching states by using the following expression:

$$\begin{bmatrix} S_A \\ S_B \\ S_C \end{bmatrix} = \begin{bmatrix} i \\ i - jc \\ i + jb \end{bmatrix} \in (0, 1, 2), \quad i \in (0, 1, 2).$$

(58)

For example, the vectors (1, -1, 0) and (0, -2, 2) in the Fig. 11 can be transformed into  $(2 \ 2 \ 1)$ ,  $(1 \ 1 \ 0)$  and  $(2 \ 0 \ 0)$  switching states respectively.

It is clear that the SVPWM based on imaginary coordinate is the simplest way in duty ratio calculations.

## VII. CONCLUSION

This paper summarizes five different SVPWM algorithms for multilevel inverters which are  $\alpha$ - $\beta$  frame, g-h frame, K-L frame,  $\alpha'$ - $\beta'$  frame and SVPWM based on imaginary coordinate system. These algorithms are general and applicable to any level of inverter. Actually SVPWM is a modulation technique which is based on line voltage. Therefore, the complex computations of conventional SVPWM are converted into simplified line voltages form as shown in TABLE II and the duty cycles calculated for all other SVPWM algorithms are compared. As an example, for validation of the calculated results, the length and the angle of reference vector was kept constant for all the SVPWM algorithms and the on-time of the corresponding vectors is calculated. The comparison results validate all the SVPWM techniques, but the SVPWM based on imaginary coordinate is the simplest one in duty ratio calculations, easier to understand and provides a better control for zero-sequence component for any level of inverter.

#### References

- L. Jih-Sheng and P. Fang Zheng, "Multilevel converters-a new breed of power converters," *IEEE Transactions on Industry Applications*, vol. 32, no. 3, pp. 509-517, 1996.

- [2] P. Fang Zheng, "A generalized multilevel inverter topology with self

voltage balancing," *IEEE Transactions on Industry Applications*, vol. 37, no. 2, pp. 611-618, 2001.

- [3] M. D. Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: a competitive solution for high-power applications," *IEEE Transactions on Industry Applications*, vol. 36, no. 3, pp. 834-841, 2000.

- [4] J. Rodriguez, L. Jih-Sheng, and P. Fang Zheng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Transactions* on *Industrial Electronics*, vol. 49, no. 4, pp. 724-738, 2002.

- [5] C. Wang and Y. Li, "A survey on topologies of multilevel converters and study of two novel topologies," in 2009 IEEE 6th International Power Electronics and Motion Control Conference, 2009, pp. 860-865.

- [6] M. A. Boost and P. D. Ziogas, "State-of-the-art carrier PWM techniques: a critical evaluation," *IEEE Transactions on Industry Applications*, vol. 24, no. 2, pp. 271-280, 1988.

- [7] J. Holtz, "Pulsewidth modulation-a survey," *IEEE Transactions on Industrial Electronics*, vol. 39, no. 5, pp. 410-420, 1992.

- [8] A. M. Hava, R. J. Kerkman, and T. A. Lipo, "Carrier-based PWM-VSI overmodulation strategies: analysis, comparison, and design," *IEEE Transactions on Power Electronics*, vol. 13, no. 4, pp. 674-689, 1998.

- [9] V. Kaura and V. Blasko, "A new method to extend linearity of a sinusoidal PWM in the overmodulation region," *IEEE Transactions on Industry Applications*, vol. 32, no. 5, pp. 1115-1121, 1996.

- [10] D. G. Holmes, "The significance of zero space vector placement for carrier-based PWM schemes," *IEEE Transactions on Industry Applications*, vol. 32, no. 5, pp. 1122-1129, 1996.

- [11] S. K. Mondal, B. K. Bose, V. Oleschuk, and J. O. P. Pinto, "Space vector pulse width modulation of three-level inverter extending operation into overmodulation region," *IEEE Transactions on Power Electronics*, vol. 18, no. 2, pp. 604-611, 2003.

- [12] V. Blasko, "Analysis of a hybrid PWM based on modified space-vector and triangle-comparison methods," *IEEE Transactions on Industry Applications*, vol. 33, no. 3, pp. 756-764, 1997.

- [13] S. R. Bowes and L. Yen-Shin, "The relationship between space-vector modulation and regular-sampled PWM," *IEEE Transactions on Industrial Electronics*, vol. 44, no. 5, pp. 670-679, 1997.

- [14] W. Fei, "Sine-triangle versus space-vector modulation for three-level PWM voltage-source inverters," *IEEE Transactions on Industry Applications*, vol. 38, no. 2, pp. 500-506, 2002.

- [15] Z. Keliang and W. Danwei, "Relationship between space-vector modulation and three-phase carrier-based PWM: a comprehensive analysis [three-phase inverters]," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 1, pp. 186-196, 2002.

- [16] W. Yao, H. Hu, and Z. Lu, "Comparisons of space-vector modulation and carrier-based modulation of multilevel inverter," *IEEE Transactions on Power Electronics*, vol. 23, no. 1, pp. 45-51, 2008.

- [17] B. P. McGrath, D. G. Holmes, and T. Lipo, "Optimized space vector switching sequences for multilevel inverters," *IEEE Transactions on Power Electronics*, vol. 18, no. 6, pp. 1293-1301, 2003.

- [18] P. N. Tekwani, R. S. Kanchan, and K. Gopakumar, "A dual five-level inverter-fed induction motor drive with common-mode voltage elimination and DC-link capacitor voltage balancing using only the switching-state redundancy—Part II," *IEEE Transactions on Industrial Electronics*, vol. 54, no. 5, pp. 2609-2617, 2007.

- [19] J. Rodriguez, J. Pontt, P. Correa, P. Cortes, and C. Silva, "A new modulation method to reduce common-mode voltages in multilevel inverters," *IEEE Transactions on Industrial Electronics*, vol. 51, no. 4, pp. 834-839, 2004.

- [20] O. Lopez, J. Alvarez, J. Doval-Gandoy, and F. D. Freijedo, "Multilevel multiphase space vector PWM algorithm with switching state redundancy," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 3, pp. 792-804, 2009.

- [21] L. M. Tolbert, P. Fang Zheng, and T. G. Habetler, "Multilevel PWM methods at low modulation indices," *IEEE Transactions on Power Electronics*, vol. 15, no. 4, pp. 719-725, 2000.

- [22] K. Xiaomin, K. A. Corzine, and Y. L. Familiant, "A unique fault-tolerant design for flying capacitor multilevel inverter," *IEEE Transactions* on *Power Electronics*, vol. 19, no. 4, pp. 979-987, 2004.

- [23] T. Bruckner and D. G. Holmes, "Optimal pulse-width modulation for

three-level inverters," *IEEE Transactions on Power Electronics*, vol. 20, no. 1, pp. 82-89, 2005.

- [24] H. Jing and K. A. Corzine, "Extended operation of flying capacitor multilevel inverters," *IEEE Transactions on Power Electronics*, vol. 21, no. 1, pp. 140-147, 2006.

- [25] M. Saeedifard, R. Iravani, and J. Pou, "Analysis and control of DC-capacitor-voltage-drift phenomenon of a passive front-end five-level converter," *IEEE Transactions on Industrial Electronics*, vol. 54, no. 6, pp. 3255-3266, 2007.

- [26] O. Bouhali, B. Francois, E. M. Berkouk, and C. Saudemont, "DC link capacitor voltage balancing in a three-phase diode clamped inverter controlled by a direct space vector of line-to-line voltages," *IEEE Transactions on Power Electronics*, vol. 22, no. 5, pp. 1636-1648, 2007.

- [27] M. Saeedifard, R. Iravani, and J. Pou, "A space vector modulation strategy for a back-to-back five-level HVDC converter system," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 2, pp. 452-466, 2009.

- [28] J. Pou, R. Pindado, D. Boroyevich, and P. Rodriguez, "Limits of the neutral-point balance in back-to-back-connected three-level converters," *IEEE Transactions on Power Electronics*, vol. 19, no. 3, pp. 722-731, 2004.

- [29] P. Zhiguo, P. Fang Zheng, K. A. Corzine, V. R. Stefanovic, J. M. Leuthen, and S. Gataric, "Voltage balancing control of diode-clamped multilevel rectifier/inverter systems," *IEEE Transactions on Industry Applications*, vol. 41, no. 6, pp. 1698-1706, 2005.

- [30] N. Celanovic and D. Boroyevich, "A comprehensive study of neutral-point voltage balancing problem in three-level neutral-pointclamped voltage source PWM inverters," *IEEE Transactions on Power Electronics*, vol. 15, no. 2, pp. 242-249, 2000.

- [31] K. Sano and H. Fujita, "Voltage-balancing circuit based on a resonant switched-capacitor converter for multilevel inverters," *IEEE Transactions on Industry Applications*, vol. 44, no. 6, pp. 1768-1776, 2008.

- [32] A. Shukla, A. Ghosh, and A. Joshi, "Flying-capacitor-based chopper circuit for DC capacitor voltage balancing in diode-clamped multilevel inverter," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 7, pp. 2249-2261, 2010.

- [33] J. Zhao, Y. Han, X. He, C. Tan, J. Cheng, and R. Zhao, "Multilevel circuit topologies based on the switched-capacitor converter and diode-clamped converter," *IEEE Transactions on Power Electronics*, vol. 26, no. 8, pp. 2127-2136, 2011.

- [34] A. Videt, P. L. Moigne, N. Idir, P. Baudesson, and X. Cimetiere, "A new carrier-based PWM providing common-mode-current reduction and DC-bus balancing for three-level inverters," *IEEE Transactions* on *Industrial Electronics*, vol. 54, no. 6, pp. 3001-3011, 2007.

- [35] J. Zaragoza, J. Pou, S. Ceballos, E. Robles, P. Ibanez, and J. L. Villate, "A comprehensive study of a hybrid modulation technique for the neutral-point-clamped converter," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 2, pp. 294-304, 2009.

- [36] J. Zaragoza, J. Pou, S. Ceballos, E. Robles, C. Jaen, and M. Corbalan, "Voltage-balance compensator for a carrier-based modulation in the neutral-point-clamped converter," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 2, pp. 305-314, 2009.

- [37] Z. Pan and F. Z. Peng, "A sinusoidal PWM method with voltage balancing capability for diode-clamped five-level converters," *IEEE Transactions on Industry Applications*, vol. 45, no. 3, pp. 1028-1034, 2009.

- [38] C. Wang and Y. Li, "Analysis and calculation of zero-sequence voltage considering neutral-point potential balancing in three-level NPC converters," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 7, pp. 2262-2271, 2010.

- [39] H. Hu, W. Yao, and Z. Lu, "Design and implementation of three-level space vector PWM IP core for FPGAs," *IEEE Transactions on Power Electronics*, vol. 22, no. 6, pp. 2234-2244, 2007.

- [40] A. R. Beig, G. Narayanan, and V. T. Ranganathan, "Modified SVP-WM algorithm for three level VSI with synchronized and symmetrical waveforms," *IEEE Transactions on Industrial Electronics*, vol. 54, no. 1, pp. 486-494, 2007.

- [41] S. Jae Hyeong, C. Chang Ho, and H. Dong Seok, "A new simplified space-vector PWM method for three-level inverters," *IEEE Transactions on Power Electronics*, vol. 16, no. 4, pp. 545-550, 2001.

- [42] A. K. Gupta and A. M. Khambadkone, "A space vector PWM scheme for multilevel inverters based on two-level space vector PWM," *IEEE Transactions on Industrial Electronics*, vol. 53, no. 5, pp. 1631-1639, 2006.

- [43] M. A. S. Aneesh, A. Gopinath, and M. R. Baiju, "A simple space vector PWM generation scheme for any general n-level inverter," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 5, pp. 1649-1656, 2009.

- [44] N. Celanovic and D. Boroyevich, "A fast space-vector modulation algorithm for multilevel three-phase converters," *IEEE Transactions* on *Industry Applications*, vol. 37, no. 2, pp. 637-641, 2001.

- [45] W. D. Jiang, S. W. Du, L. C. Chang, Y. Zhang, and Q. Zhao, "Hybrid PWM strategy of SVPWM and VSVPWM for NPC three-level voltage-source inverter," *IEEE Transactions on Power Electronics*, vol. 25, no. 10, pp. 2607-2619, 2010.

- [46] A. Gopinath, M. A. S. Aneesh, and M. R. Baiju, "Fractal based space vector pwm for multilevel inverters—A novel approach," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 4, pp. 1230-1237, 2009.

- [47] Y. Li, Y. Gao, and X. Hou, "A general SVM algorithm for multilevel converters considering zero-sequence component control," in 31st Annual Conference of IEEE Industrial Electronics Society, 2005. IECON 2005., 2005, p. 6.

- [48] X. -N. Xiao, X. Jiang, H. Liu, H. -W. Liu, and S.-L. Kong, "Study on the SVPWM algorithm of N-level inverter in the context of non-orthogonal coordinates," *Frontiers of Electrical and Electronic Engineering in China*, vol. 1, no. 2, pp. 199-204, Jun. 2006.

- [49] B. Fan, G. Tan, and S. Fan, "Comparison of three different 2-d space vector pwm algorithms and their fpga implementations," *Journal of Power Technologies*, vol. 94, no. 3, p. 176, 2014.

- [50] R. Zhu, X. Wu, and Y. Tang, "Duty cycle-based three-level space-vector pulse-width modulation with overmodulation and neutral-point balancing capabilities for three-phase neutral-point clamped inverters," *IET Power Electronics*, vol. 8, no. 10, pp. 1931-1940, 2015.

- [51] Z. Shu, N. Ding, J. Chen, H. Zhu, and X. He, "Multilevel SVPWM with DC-link capacitor voltage balancing control for diode-clamped multilevel converter based STATCOM," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 5, pp. 1884-1896, 2013.

- [52] D. Peng, F. C. Lee, and D. Boroyevich, "A novel SVM algorithm for multilevel three-phase converters," in *Power Electronics Specialists Conference, 2002. Pesc 02. 2002 IEEE 33rd Annual*, 2002, vol. 2, pp. 509-513.

**Yongdong Li** was born in Hebei Province, China, in 1962. He received the B.S. degree in electrical engineering from Harbin Institute of Technology, Harbin, China, in 1982 and the M.S. and Ph.D. degrees in electrical engineering from the Institut National Polytechnique de Toulouse, Toulouse, France, in 1984 and 1987, respectively.

He was a Postdoctoral Researcher from 1988 to 1990 and an Associate Professor from 1991 to 1996 with the Department of Electrical Engineering, Ts-

inghua University, Beijing, China. Since 1996, he has been a Professor with the same department of Tsinghua University. He is currently responsible of Laboratory of Power Electronics and Motor Control, Tsinghua University. His research interests include high voltage power electronic converters and their applications in variable speed drives for energy saving, digital control, sensor-less drives of AC motors and their applications in NC machine-tools, traction drives for high speed train and propulsion drives for ships, renewable energy generation, like wind, solar, etc. He's got the honors of "Delta Scholar" in 2003, "Tianshan Scholar" in 2013, and "Excellent Professor and Good Friend" of students of Tsinghua University several times. He is author of 3 Monographs, more than 300 papers in national and international conferences and journals, including more than 100 papers indexed by SCI and EL

Dr. Li has been vice-director of Electrical Machine and Control Group of Dept. of Electrical Engineering, Tsinghua University, vice-director of National Key Lab. of Control and Simulation of Power System and large generator, director of Power Electronics and Motor Control Lab., and is currently deputy director of Power Electronic Engineering Research Center of Tsinghua University, and IEEE IAS Beijing Chapter Chairman, vice-chairman of China Power Electronics Society, vice-chairman of Electrical Automation Committee of China Automation Association, member of board of directors of PCIM Asia.

Qamar Muhammad Attique was born in Faisalabad, Pakistan, in 1988. He received the B.Sc degree in electronics engineering from COMSATS Institute of Information Technology, Abbottabad, Pakistan, in 2012, and M.Sc degree in control science and engineering from Beijing Institute of Technology, Beijing, China, in 2016.

He is currently pursuing the Ph.D. degree in electrical engineering at Tsinghua University, Beijing, China. His research interests include multilev-

el inverters and pulse width modulation techniques.

Kui Wang was born in Hubei, China, in 1984. He received the B.S. and Ph.D. degrees in Electrical Engineering from the Department of Electrical Engineering, Tsinghua University, Beijing, China, in 2006 and 2011, respectively.

He is currently an Assistant Researcher with the Department of Electrical Engineering, Tsinghua University. His research interests include topology and control of multilevel converters, renewable energy generation and wide band-gap semiconductor.