# A Novel Space Vector Modulation Scheme for Common-Mode Voltage Reduction in the Hybrid Active Neutral-Point-Clamped Three-Level Inverter with Balanced and Unbalanced DC-Links

Chuanjing HOU, Desheng JIA, Changwei QIN, Xiaoyan LI, and Jiandong LI

**Abstract**—The hybrid active neutral-point-clamped (HANPC) three-level inverter (TLI) requires much less SiC MOSFETs than a full-SiC ANPC TLI while providing comparable power density. Therefore, the HANPC TLI is an ideal solution for balancing performance and cost. However, excessive common-mode voltage (CMV) amplitudes are observed in conventional modulation methods, especially under unbalanced DC-links. This paper presents a CMV reduction method for the HANPC TLI with balanced and unbalanced DC-links. The scheme employs real-time sampling of photovoltaic array voltages on the DC side, followed by dynamic updates to the space vector diagram (SVD). Due to its inherent advantage of low CMV, zero vector and medium vectors are selected for reference vector synthesis. According to the position of the medium vectors in the updated SVD, the duty cycles are recalculated to ensure the output current quality. Furthermore, switching sequences are optimized through five-segment symmetrical patterning, ensuring minimal switching actions in power devices. Theoretical analysis demonstrates that this modulation method effectively reduces both the magnitude and root-mean-square (RMS) value of CMV while ensuring that SiC MOSFETs and Si IGBTs operate at high and low frequencies, respectively. The hardware-in-loop (HIL) tests validate the efficacy of the proposed modulation strategy.

**Index Terms**—Common-mode voltage, hybrid active neutral-point-clamped (HANPC), silicon carbide (SiC), unbalanced DC-links.

## I. INTRODUCTION

THREE-LEVEL inverters (TLI) are recognized as fundamental components in modern power conversion sys-

Manuscript received June 16, 2025; revised August 3, 2025; accepted August 24, 2025. Date of publication December 30, 2025; date of current version September 9, 2025. This work was supported by the Taishan Scholar Project of Shandong Province under the grant tsqn202312223, the Natural Science Foundation of Shandong Province under the grant ZR2024MF039 and grant ZR2025MS1051, the National Natural Science Foundation of China under the grant 62573273, and the Development Plan for Youth Innovation Team of Higher Education Institutions in Shandong Province under the grant 2023KJ127. (Corresponding authors: Changwei Qin and Xiaoyan Li.)

All authors are with the School of Information and Electrical Engineering, Shandong Jianzhu University, Jinan 250101, China, and Shandong Key Laboratory of Smart Buildings and Energy Efficiency, Jinan 250101, China (e-mail: houchuanjing1211@sdjzu.edu.cn; 2022085101@stu.sdjzu.edu.cn; qinchangwei20@sdjzu.edu.cn; xylee2023@sdjzu.edu.cn; 2023080127@stu.sdjzu.edu.cn).

Digital Object Identifier 10.24295/CPSSTPEA.2025.00033

tems, particularly in renewable energy applications, due to their superior performance over conventional two-level topologies [1], [2]. By generating three distinct voltage levels, these inverters significantly reduce voltage stress on switching devices, minimize output harmonic distortion, and lower electromagnetic interference (EMI) [3]–[5]. These characteristics enable enhanced system efficiency and improved power quality. Reliable operation is ensured for grid-connected photovoltaic (PV) systems.

The hybrid active neutral-point-clamped (HANPC) TLI topology is recognized as an advanced power electronic configuration. Compared with conventional neutral-point-clamped (NPC) inverters, diodes are replaced by active switching devices in HANPC implementations. Improved loss distribution uniformity is achieved through this structural modification. The reduced conduction voltage across switching devices is obtained. Consequently, operational efficiency and power density are elevated [6]–[8].

In the HANPC topology, each phase leg is typically constructed with six switching devices. Four low-frequency switches and two high-frequency switches are integrated in this configuration. Such a configuration makes the inverter more flexible in control and able to adapt to different loads and working conditions requirements. It enables it to have a wide range of application prospects and advantages in high-voltage high-power power electronics applications [9], [10].

In PV systems, however, the advantages of HANPC inverters are often challenged by inherent DC-links voltage imbalances. Such imbalances arise from partial shading, module degradation, or mismatched string configurations in solar arrays [11]–[13]. These conditions lead to unequal power generation across PV strings, causing asymmetric voltage distribution in the DC-links capacitors, the presence of unbalanced neutral-point voltage can degrade the overall performance of both the equipment and the grid [14].

Under severe imbalance, the neutral-point voltage oscillates excessively, amplifying common-mode voltage (CMV) and inducing leakage currents through the parasitic capacitance between PV panels and ground [15]–[17]. Elevated CMV not only degrades system efficiency but also poses safety risks, accelerates component aging, and violates grid codes for

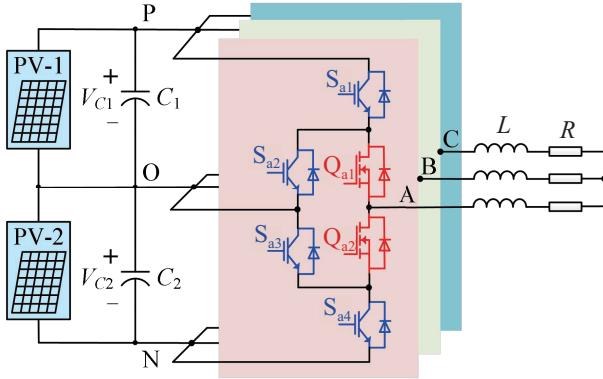

Fig. 1. Topology of the HANPC TLI with unbalanced DC-links.

electromagnetic compatibility (EMC) [18], [19]. Traditional CMV mitigation strategies, such as passive filters or complex modulation schemes, often introduce trade-offs between hardware complexity, efficiency, and current quality [20]. For instance, passive damping resistors reduce CMV at the expense of increased losses, while advanced modulation methods like virtual vector synthesis may compromise dynamic response or require excessive computational resources [21]–[23]. [24] presents a space vector modulation (SVM) strategy for suppressing the CMV in the reduced switch count (RSC) TLI with unbalanced neutral-point voltage, due to topological limitations, this method abandons the medium vector with a lower CMV amplitude. [25] proposes an optimized DPWM (O-DPWM) scheme to reduce the leakage current for three-level inverters under different neutral-point voltage conditions. The proposed method has demonstrated effective suppression of leakage current under unbalanced operating conditions, while exhibiting limited effectiveness in common-mode voltage suppression.

To this end, this paper presents a novel CMV suppression strategy for the HANPC TLI, which is applicable for both balanced and imbalanced DC-links capacitor voltage conditions. Real-time sampling of DC-links capacitor voltages enables continuous updates to the space vector diagram. A revised duty cycle calculation algorithm is introduced. The core innovation lies in the comprehensive utilization of medium vectors for reference voltage vector synthesis.

The remainder of this paper is organized as follows: Section II presents the topology and working principles of the HANPC TLI. Section III introduces the proposed modulation scheme. Section IV gives comprehensive experimental results to verify the correctness and effectiveness of the proposed method. Finally, Section V concludes this article.

## II. WORKING PRINCIPLE OF HANPC TLI WITH BALANCED AND UNBALANCED DC-LINKS

In this section, a detailed presentation of the HANPC TLI topology is given, which includes topology structure and operational principles. Fig. 1 shows the general circuit of HANPC TLI, each capacitor is connected to a PV array at

TABLE I

OUTPUT STATES AND OUTPUT VOLTAGES CORRESPONDING TO SWITCHING STATES OF HANPC TLI

| Output state | Output voltage | Switching states ( $x = a, b, c$ ) |          |          |          |          |          |

|--------------|----------------|------------------------------------|----------|----------|----------|----------|----------|

|              |                | $S_{x1}$                           | $S_{x2}$ | $S_{x3}$ | $S_{x4}$ | $Q_{x1}$ | $Q_{x2}$ |

| [P]          | $V_{c1}$       | 1                                  | 0        | 1        | 0        | 1        | 0        |

| [O-]         | 0              |                                    | 1        | 0        | 1        | 0        | 1        |

| [O-]         | 0              |                                    | 0        | 1        | 0        | 1        | 0        |

| [N]          | $-V_{c2}$      | 0                                  | 1        | 0        | 1        | 0        | 1        |

TABLE II

BASIC VOLTAGE VECTORS AND CMVs FOR HANPC TLI WITH UNBALANCED DC-LINKS

| Vectors | State          | CMV                   | State | CMV                  |

|---------|----------------|-----------------------|-------|----------------------|

| Zero    | [PPP]<br>[NNN] | $V_{c1}$<br>$-V_{c2}$ | [OOO] | 0                    |

| P-Type  | [POO]          | $V_{c1}/3$            | [PPO] | $2V_{c1}/3$          |

| Small   | [OPO]          | $V_{c1}/3$            | [POP] | $2V_{c1}/3$          |

|         | [OOP]          | $V_{c1}/3$            | [OPP] | $2V_{c1}/3$          |

| N-Type  | [NOO]          | $-V_{c2}/3$           | [NNO] | $-2V_{c2}/3$         |

| Small   | [ONO]          | $-V_{c2}/3$           | [NON] | $-2V_{c2}/3$         |

|         | [OON]          | $-V_{c2}/3$           | [ONN] | $-2V_{c2}/3$         |

| Medium  | [PON]          | $(V_{c1}-V_{c2})/3$   | [OPN] | $(V_{c1}-V_{c2})/3$  |

|         | [NPO]          | $(V_{c1}-V_{c2})/3$   | [NOP] | $(V_{c1}-V_{c2})/3$  |

|         | [ONP]          | $(V_{c1}-V_{c2})/3$   | [PNO] | $(V_{c1}-V_{c2})/3$  |

|         | [NNP]          | $(V_{c1}-2V_{c2})/3$  | [PNP] | $(2V_{c1}-V_{c2})/3$ |

| Large   | [NPN]          | $(V_{c1}-2V_{c2})/3$  | [NPP] | $(2V_{c1}-V_{c2})/3$ |

|         | [PNN]          | $(V_{c1}-2V_{c2})/3$  | [PPN] | $(2V_{c1}-V_{c2})/3$ |

both ends [26]. The capacitor voltage is denoted by  $V_{c1}$  and  $V_{c2}$ , respectively. The HANPC TLI comprises four Si IGBTs switches ( $S_{x1}$ ,  $S_{x2}$ ,  $S_{x3}$ , and  $S_{x4}$ ) and two SiC MOSFETs switches ( $Q_{x1}$  and  $Q_{x2}$ ) ( $x=a, b, c$ ) in each phase.

Table I summarizes the output states and voltage levels corresponding to all switching states of the HANPC TLI, where “1” and “0” represent the on and off states of semiconductors, respectively. It should be noted that the NPC TLI merely has three output states [P], [N], and [O], the HANPC topology contains four output states [P], [N], [O<sub>+</sub>], and [O<sub>-</sub>].

The CMV calculation formula is calculated as follows:

$$v_{CM} = \frac{v_{AO} + v_{BO} + v_{CO}}{3} \quad (1)$$

where  $v_{AO}$ ,  $v_{BO}$ , and  $v_{CO}$  are three-phase output voltages. All the basic voltage vectors are summarized in Table II. Obviously, the basic vectors marked in red exhibit the highest CMV magnitudes and should therefore be excluded during reference vector synthesis. Conversely, the vectors highlighted in blue generating minimal CMV and are prioritized in the proposed space vector modulation scheme to achieve effective CMV suppression. Based on this analysis, a systematic CMV mitigation strategy for the HANPC TLI under both balanced and unbalanced DC-links capacitor voltage conditions will be

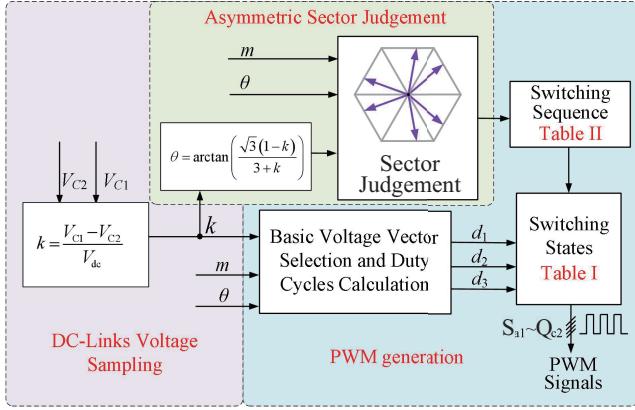

Fig. 2. Overall diagram of the proposed novel modulation method.

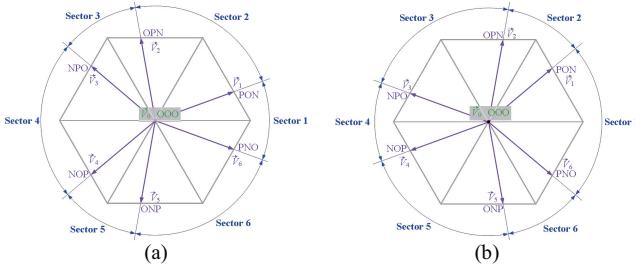

Fig. 3. SVDs for HANPC TLI with unbalanced DC-links. (a)  $k > 0$ , (b)  $k < 0$ .

elaborated in the following section.

### III. PROPOSED MODULATION STRATEGY

The proposed modulation strategy consists of three components. Initially, the two capacitor voltages on the DC-links are sampled, and the capacitor voltage unbalance factor  $k$  is calculated by the formula. Subsequently, the space vector diagram (SVD) is updated according to the capacitor voltage imbalance factor for sector judgment of the reference voltage vector ( $V_{ref}$ ). Finally, the duty cycle is calculated based on the capacitor voltage unbalance factor, and the drive signal of the power switching tube is generated based on the corresponding switching sequence. The overall diagram of the proposed method is shown in Fig. 2.

#### A. DC-Links Voltage Sampling and Sector Judgement

Firstly, the voltages across capacitors  $C_1$  and  $C_2$  are sampled, and noted as  $V_{c1}$  and  $V_{c2}$ , respectively.

Next, the unbalanced factor  $k$  is defined as:

$$k = (V_{c1} - V_{c2}) / V_{dc} \quad (2)$$

Under unbalanced neutral point (NP) voltage conditions, the capacitor voltage fluctuates in response to variations in the voltages of the two PV arrays, resulting in a corresponding alteration of the SVD, as illustrated in Fig. 3. Consequently, the medium vector expression can be represented by the following equation:

$$\left\{ \begin{array}{l} \vec{V}_1 \text{ [PON]} = \frac{3+k}{6} \cdot V_{dc} + j \cdot \frac{\sqrt{3} \cdot (1-k)}{6} \cdot V_{dc} \\ \vec{V}_2 \text{ [OPN]} = -\frac{k}{3} \cdot V_{dc} + j \cdot \frac{\sqrt{3}}{3} \cdot V_{dc} \\ \vec{V}_3 \text{ [NPO]} = \frac{k-3}{6} \cdot V_{dc} + j \cdot \frac{\sqrt{3} \cdot (1+k)}{6} \cdot V_{dc} \\ \vec{V}_4 \text{ [NOP]} = \frac{k-3}{6} \cdot V_{dc} - j \cdot \frac{\sqrt{3} \cdot (1+k)}{6} \cdot V_{dc} \\ \vec{V}_5 \text{ [ONP]} = -\frac{k}{3} \cdot V_{dc} - j \cdot \frac{\sqrt{3}}{3} \cdot V_{dc} \\ \vec{V}_6 \text{ [PNO]} = \frac{3+k}{6} \cdot V_{dc} - j \cdot \frac{\sqrt{3} \cdot (1-k)}{6} \cdot V_{dc} \end{array} \right. \quad (3)$$

Since the position of the medium vector in the SVD will change with the capacitor voltage offset on the DC-links, it is necessary to compute the position of the medium vector in real time when judging sectors, and the angle of the medium vector [PON] can be calculated by the following formula:

$$\theta = \arctan \left( \frac{\sqrt{3} (1-k)}{3+k} \right) \quad (4)$$

#### B. Duty Cycle Calculation and Drive Signals Generation

Taking Sector 1 as an example, two fundamental voltage vectors [PON] and [PNO] are used to synthesize the reference voltage vector. The voltage-second balance equation is written as follows:

$$\left\{ \begin{array}{l} \vec{V}_{ref} = \vec{V}_1 \cdot d_1 + \vec{V}_6 \cdot d_6 + \vec{V}_0 \cdot d_0 \\ d_1 + d_6 + d_0 = 1 \end{array} \right. \quad (5)$$

where  $d_1$ ,  $d_6$ , and  $d_0$  are the duty cycle of [PON], [PNO], and [OOO].

The corresponding duty cycle can be calculated as:

$$\left\{ \begin{array}{l} d_1 = m \cdot \frac{\sqrt{3}}{3+k} \cdot \cos \theta + m \cdot \frac{1}{1-k} \cdot \sin \theta \\ d_6 = m \cdot \frac{\sqrt{3}}{3+k} \cdot \cos \theta - m \cdot \frac{1}{1-k} \cdot \sin \theta \\ d_0 = 1 - m \cdot \frac{2\sqrt{3}}{3+k} \cdot \cos \theta \end{array} \right. \quad (6)$$

Considering the symmetry of SVD, the duty cycle formulas in other sectors are similar to the above analysis and will not be repeated here.

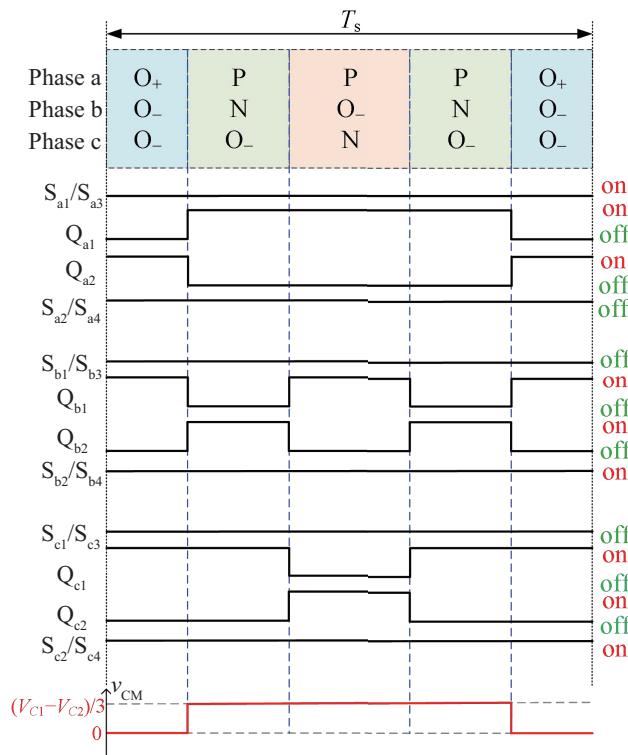

In Sector 1, to satisfy the requirements of reduced switching numbers and harmonic distortions, the switching sequence is arranged as [O<sub>+</sub>O O<sub>-</sub>]-[PNO]-[PO N]-[PNO]-[O<sub>+</sub>O O<sub>-</sub>], as shown in Fig. 4. Within each sampling period, the switching states of all Si IGBTs ( $S_{a1}$ - $S_{e4}$ ) are maintained unchanged, thereby avoiding additional switching losses. For the SiC

TABLE III

SWITCHING SEQUENCE OF THE PROPOSED METHOD

| Sector | Switching sequence                     |

|--------|----------------------------------------|

| 1      | [O-O-O-]-[PNO-]-[PO-N]-[PNO-]-[O-O-O-] |

| 2      | [O-O-O-]-[PO+N]-[O+PN]-[PO+N]-[O-O-O-] |

| 3      | [O-O-O-]-[O-PN]-[NPO-]-[O-PN]-[O-O-O-] |

| 4      | [O-O-O-]-[NO+P]-[NPO+]-[NO-P]-[O-O-O-] |

| 5      | [O-O-O-]-[O-NP]-[NO-P]-[O-NP]-[O-O-O-] |

| 6      | [O-O-O-]-[O+NP]-[PNO+]-[O+NP]-[O-O-O-] |

Fig. 4. Switching sequence, switching states, and CMV in Sector 1,  $k>0$ .

MOSFETs, the power devices of phase a and phase c undergo a single switching action per cycle, while the power devices of phase b exhibit two switching actions. Similar switching patterns are observed in other sectors. Furthermore, zero vector produces zero CMV, whereas the medium vectors generate a smaller CMV amplitude of only  $(V_{ci} - V_{c2})/3$ .

By designing a reasonable modulation strategy, the SiC MOSFETs can operate in high-frequency and the Si IGBTs can operate in fundamental frequency, which further reduces switching losses, and thus improves system efficiency. Table III summarizes the switching sequences in all sectors for the proposed modulation strategy.

#### IV. EXPERIMENTAL RESULTS

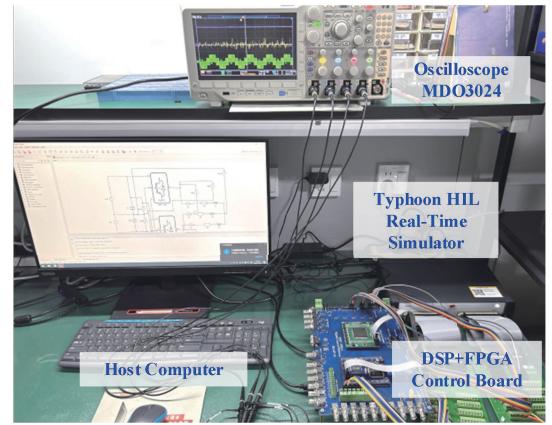

To validate the performance of the proposed modulation scheme, an experimental test system of the HANPC TLI is designed, as shown in Fig. 5. The main circuit is implemented

TABLE IV

PARAMETERS FOR EXPERIMENTAL TEST

| Parameter                              | Value                                               |

|----------------------------------------|-----------------------------------------------------|

| DC Voltage ( $V_{dc}$ )                | 540 V                                               |

| AC output frequency ( $f$ )            | 50 Hz                                               |

| Switching period ( $T_s$ )             | 100 $\mu$ s                                         |

| Sampling frequency ( $f_{sf}$ )        | 10 kHz                                              |

| DC-link capacitors ( $C_1$ and $C_2$ ) | 2350 $\mu$ F                                        |

| Voltage difference                     | -100 V, 0 V, 100 V                                  |

| $RL$ load                              | $R_{load} = 10 \Omega$<br>$L_{load} = 7 \text{ mH}$ |

Fig. 5. Photograph of the hardware-based test rig.

based on hardware-in-the-loop (HIL) real-time simulator. The control board is designed to contain digital signal processor (DSP) 28335 from Texas Instruments and field-programmable gate array (FPGA) XC3S500E from Xilinx. The DSP is used to execute the system control strategy, while the FPGA is used to generate the PWM signals. The DSP sends data to the FPGA through an external interface (XINTF) module, which includes the sector number and the duty cycle.

The parameters for both simulation and experimental tests are given in Table IV. To demonstrate the significant advantages of the proposed modulation strategy, three modulation methods suitable for unbalanced conditions are used for comparisons. Method-1 is the hybrid SVM method in [27], method-2 is the CMV reduction method in [28], and method-3 is the proposed CMV reduction scheme.

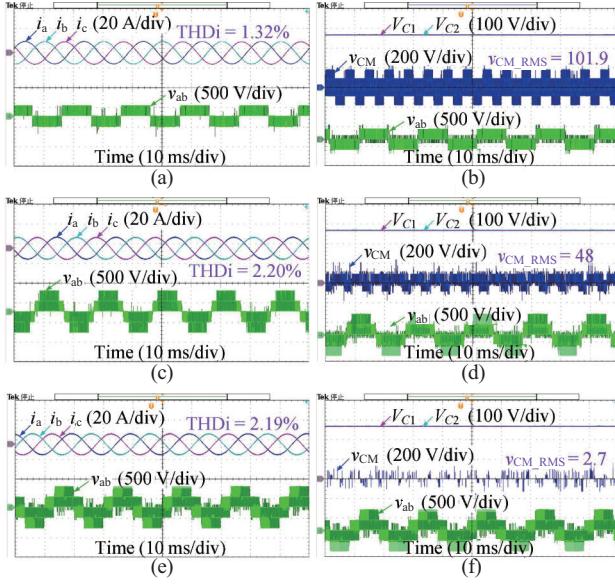

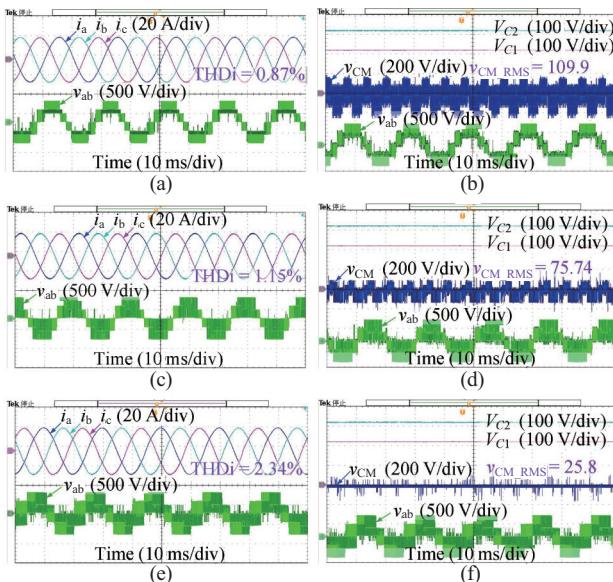

The first verification is the operation of the three modulation methods in the balanced conditions, and the experimental results are shown in Fig. 6, in which the modulation index  $m$  is 0.4 and the voltage difference between two DC-links capacitors is set to be 270 V. The CMVs of method-1 and method-2 are relatively high, because the basic vectors with high CMV magnitudes are utilized by these two methods.

Since method-1 uses all the basic vectors to synthesize the  $V_{ref}$ , it achieves an output current total harmonic distortion (THD) of only 1.32%. However, this method exhibits significantly higher CMV amplitudes, with a peak-to-peak range of 360 V

Fig. 6. Experimental results under balanced conditions ( $m = 0.4, k = 0$ ). (a) Three-phase output currents and line voltage of Method-1, (b) DC power source voltage and common-mode voltage of Method-1, (c) Three-phase output currents and line voltage of Method-2, (d) DC power source voltage and common-mode voltage of Method-2, (e) Three-phase output currents and line voltage of Method-3, (f) DC power source voltage and common-mode voltage of Method-3.

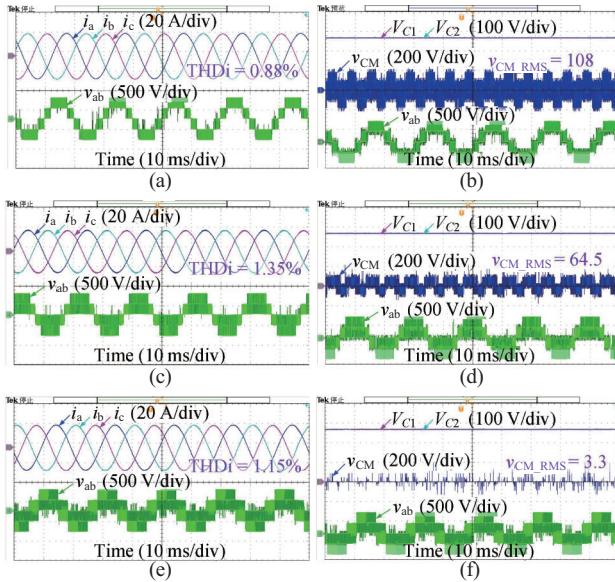

Fig. 7. Experimental results under balanced conditions ( $m = 0.8, k = 0$ ). (a) Three-phase output currents and line voltage of Method-1, (b) DC power source voltage and common-mode voltage of Method-1, (c) Three-phase output currents and line voltage of Method-2, (d) DC power source voltage and common-mode voltage of Method-2, (e) Three-phase output currents and line voltage of Method-3, (f) DC power source voltage and common-mode voltage of Method-3.

( $-178$  V to  $182$  V) and an RMS value of  $101.9$  V. Method-2 optimizes vector selection by eliminating small vectors with high CMV amplitudes, reducing the CMV RMS value to  $48$  V while maintaining an output current THD of  $2.20\%$ .

The proposed method-3 adopts a medium-vector-dominated synthesis scheme, theoretically achieving zero CMV under

TABLE V

COMPARISONS OF DIFFERENT METHODS UNDER BALANCED CONDITIONS

| Conditions | Range of CMV | RMS value of CMV     | THDi      |

|------------|--------------|----------------------|-----------|

| Method-1   | $m = 0.4$    | $-178$ V ~ $182$ V   | $101.9$ V |

|            | $m = 0.8$    | $-179$ V ~ $182$ V   | $108$ V   |

| Method-2   | $m = 0.4$    | $-85.2$ V ~ $91.5$ V | $48$ V    |

|            | $m = 0.8$    | $-85$ V ~ $91$ V     | $64.5$ V  |

| Method-3   | $m = 0.4$    | $0$ V                | $2.7$ V   |

|            | $m = 0.8$    | $0$ V                | $3.3$ V   |

balanced conditions. Experimental results confirm its CMV RMS value as low as  $2.7$  V, with an output current THD of  $2.19\%$ , demonstrating a synergistic optimization of CMV suppression and current quality. The proposed method can effectively suppress the CMV, whereas three-phase sinusoidal output currents can be guaranteed at the same time.

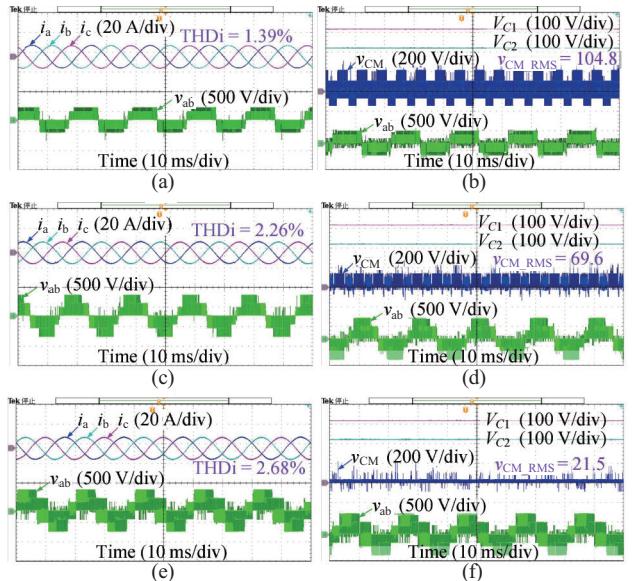

To further validate the adaptability of modulation strategies, experiments were repeated at a higher modulation index ( $m=0.8$ ). As illustrated in Fig. 7, all three methods maintain stable operation under high modulation index conditions, with CMV suppression characteristics consistent with those observed at low modulation. Notably, method-3 restricts the CMV RMS value to  $3.3$  V and reduces the output current THD to  $1.15\%$ , confirming its applicability across a wide modulation index range. A systematic comparison of CMV suppression and THD performance under balanced DC-links conditions is summarized in Table V. Since method-3 avoids using the basic voltage vectors with high CMV magnitudes, the current THD value is slightly higher than that of method-1 and method-2. Fortunately, the current THD value of the proposed method remains at an acceptable level.

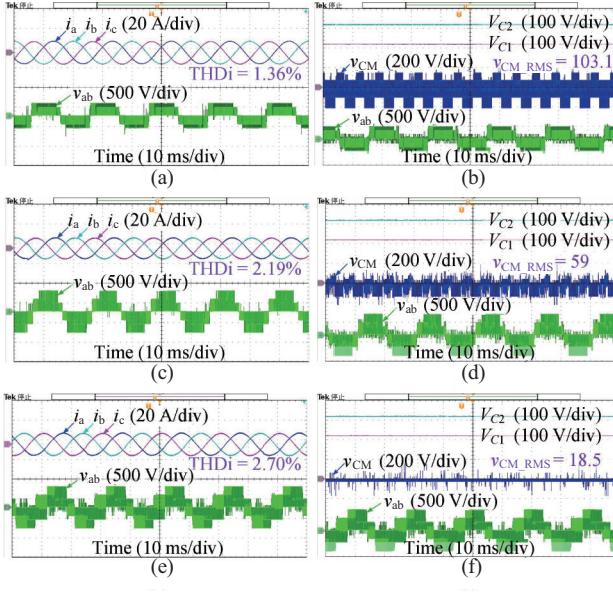

For DC-links voltage imbalance conditions, experiments were conducted with  $\pm 100$  V deviations ( $k=\pm 0.1852$ ). As shown in Fig. 8, when the upper capacitor voltage is  $100$  V lower than the lower capacitor ( $k=-0.1852$ ) at  $m=0.4$ , method-1 exhibits a CMV peak-to-peak range of  $358.5$  V ( $-211.5$  V to  $147$  V) and an RMS value of  $103.1$  V, accompanied by a THD of  $1.36\%$ . Method-2 reduces the CMV RMS value to  $59$  V with a THD of  $2.19\%$ , while method-3 leverages the inherent low-CMV characteristics of medium vectors, achieving a CMV RMS value of  $18.5$  V and a THD of  $2.7\%$ .

At  $m=0.8$  (Fig. 9), method-3 increases the CMV RMS value slightly to  $25.8$  V but further reduces the THD to  $2.34\%$ , demonstrating effective CMV suppression and high-quality current output under imbalanced conditions. Quantitative comparisons under these conditions are systematically presented in Table VI.

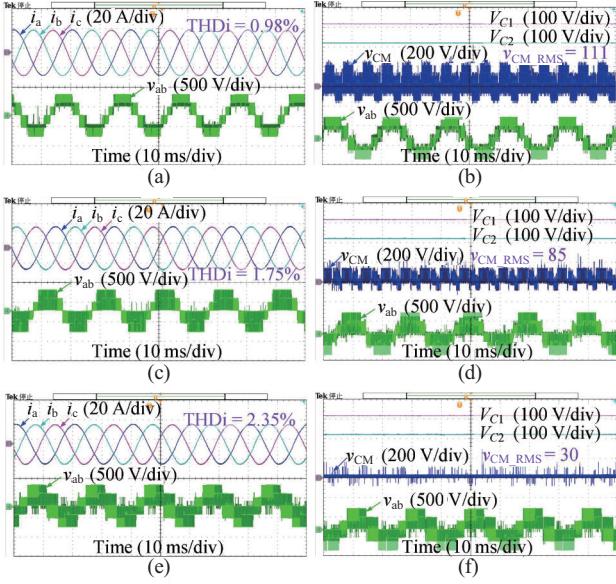

When the upper capacitor voltage exceeds the lower capacitor by  $100$  V ( $k = 0.1852$ ), the experimental waveforms for the case of low and high modulation indices ( $m=0.4$  and  $m=0.8$ ) are shown in Fig. 10 and Fig. 11, respectively. The CMV suppression performance and output current quality remain consistent with those under negative imbalance conditions. Although the proposed method exhibits marginal THD degradation compared to method-1, it demonstrates a significant

Fig. 8. Experimental results for negative unbalancing coefficient ( $m = 0.4$ ,  $k = -0.1852$ ). (a) Three-phase output currents and line voltage of Method-1, (b) DC power source voltage and common-mode voltage of Method-1, (c) Three-phase output currents and line voltage of Method-2, (d) DC power source voltage and common-mode voltage of Method-2, (e) Three-phase output currents and line voltage of Method-3, (f) DC power source voltage and common-mode voltage of Method-3.

Fig. 9. Experimental results for negative unbalancing factor ( $m = 0.8$ ,  $k = -0.1852$ ). (a) Three-phase output currents and line voltage of Method-1, (b) DC power source voltage and common-mode voltage of Method-1, (c) Three-phase output currents and line voltage of Method-2, (d) DC power source voltage and common-mode voltage of Method-2, (e) Three-phase output currents and line voltage of Method-3, (f) DC power source voltage and common-mode voltage of Method-3.

advantage in CMV amplitude reduction. The quantitative performance for positive unbalancing factor is summarized in Table VII.

Overall, method-3 effectively reduces the CMV amplitude and RMS value under different modulation indexes and

TABLE VI

COMPARISONS OF DIFFERENT METHODS FOR NEGATIVE UNBALANCING FACTOR ( $k = -0.1852$ )

| Conditions | Range of CMV | RMS value of CMV    | THDi    |

|------------|--------------|---------------------|---------|

| Method-1   | $m = 0.4$    | $-211.5 \sim 147$ V | 103.1 V |

|            | $m = 0.8$    | $-211.5 \sim 147$ V | 109.9 V |

| Method-2   | $m = 0.4$    | $-136 \sim 73$ V    | 59 V    |

|            | $m = 0.8$    | $-135.5 \sim 73$ V  | 75.74 V |

| Method-3   | $m = 0.4$    | $-28 \sim 0$ V      | 18.5 V  |

|            | $m = 0.8$    | $-28 \sim 0$ V      | 25.8 V  |

Fig. 10. Experimental results for positive unbalancing factor ( $m = 0.4$ ,  $k = 0.1852$ ). (a) Three-phase output currents and line voltage of Method-1, (b) DC power source voltage and common-mode voltage of Method-1, (c) Three-phase output currents and line voltage of Method-2, (d) DC power source voltage and common-mode voltage of Method-2, (e) Three-phase output currents and line voltage of Method-3, (f) DC power source voltage and common-mode voltage of Method-3.

different unbalance factors, thus ensuring the safe and stable operation of the inverter system.

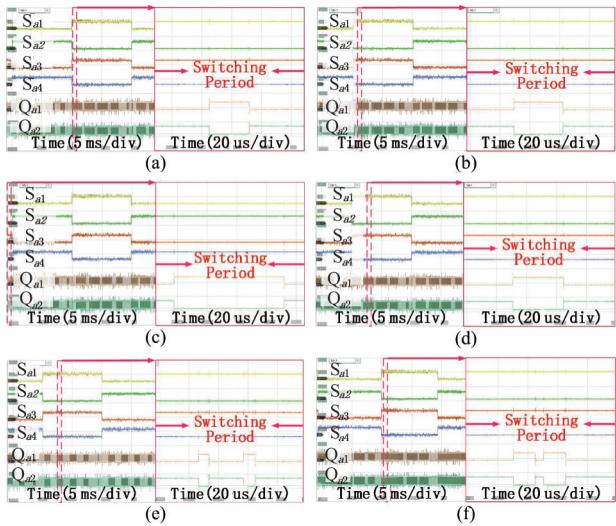

Selected experimental waveforms of the power switch drive signals are depicted in Fig. 12. All three modulation methods achieved hybrid high-low frequency modulation. Method-1 and method-2 generate only one switching action per phase per cycle, whereas method-3 introduces optimized medium-vector timing to achieve precise CMV control, resulting in two switching actions for one phase while maintaining single switching actions for the other two phases, consistent with theoretical predictions. This design ensures minimal additional switching losses while prioritizing CMV suppression.

To verify the influence of unbalanced conditions on the DC side on the loss distribution, a co-simulation platform of Simulink and PLECS was built for the proposed common-mode voltage suppression method, and the corresponding losses were calculated and summarized in Fig. 13. It can be seen from the figure that under balanced conditions, due to its symmetrical

Fig. 11. Experimental results for positive unbalancing factor ( $m = 0.8$ ,  $k = 0.1852$ ). (a) Three-phase output currents and line voltage of Method-1, (b) DC power source voltage and common-mode voltage of Method-1, (c) Three-phase output currents and line voltage of Method-2, (d) DC power source voltage and common-mode voltage of Method-2, (e) Three-phase output currents and line voltage of Method-3, (f) DC power source voltage and common-mode voltage of Method-3.

TABLE VII

COMPARISONS OF DIFFERENT METHODS FOR NEGATIVE

UNBALANCING FACTOR ( $k = 0.1852$ )

| Conditions | Range of CMV                                      | RMS value of CMV | THDi   |

|------------|---------------------------------------------------|------------------|--------|

| Method-1   | $m = 0.4$ $-142.5 \text{ V} \sim 217.5 \text{ V}$ | 104.8 V          | 1.39 % |

|            | $m = 0.8$ $-143 \text{ V} \sim 217 \text{ V}$     | 111 V            | 0.98 % |

| Method-2   | $m = 0.4$ $-68 \text{ V} \sim 140 \text{ V}$      | 69.6 V           | 2.26 % |

|            | $m = 0.8$ $-68 \text{ V} \sim 141.5 \text{ V}$    | 85 V             | 1.75 % |

| Method-3   | $m = 0.4$ $0 \text{ V} \sim 33 \text{ V}$         | 21.5 V           | 2.68 % |

|            | $m = 0.8$ $0 \text{ V} \sim 32.5 \text{ V}$       | 30 V             | 2.35 % |

Fig. 12. Drive signals of power switches. (a) method-1,  $m = 0.8$ ,  $k = 0$ , (b) method-1,  $m = 0.8$ ,  $k = 0.1852$ , (c) method-2,  $m = 0.8$ ,  $k = 0$ , (d) method-2,  $m = 0.8$ ,  $k = 0.1852$ , (e) method-3,  $m = 0.8$ ,  $k = 0$ , (f) method-3,  $m = 0.8$ ,  $k = 0.1852$ .

characteristics, the conduction loss and switching loss of power devices can remain relatively balanced. Under the unbalanced condition on the DC-links, when  $k = 0.1852$ , the increase in the voltage of the lower capacitor  $C_2$  will increase the switching loss of the power device  $Q_{a2}$ , but the overall loss can remain relatively balanced. The same conclusion can be extended to other conditions.

## V. CONCLUSION

For the dual-input TLI system, this paper presents a novel CMV reduction method for HANPV TLI with balanced and unbalanced NP voltage conditions. This method eliminates vectors with higher CMV amplitudes. By sampling the DC-links capacitor voltages, an imbalance factor is calculated, which subsequently facilitates the reconfiguration of the SVD, thereby simplifying the computational complexity. Furthermore, a symmetrical five-segment switching sequence that starts and ends with zero vector is designed to reduce harmonics. Experiments verify the effectiveness of the proposed modulation strategy.

## REFERENCES

- [1] C. Zhang, *Advanced Control of Grid-Connected High-Power Converters*, Singapore: Springer Nature Singapore, 2023.

- [2] C. Hou, D. Jia, C. Qin, and X. Li, "A novel topology and modulation strategy for the high-gain hybrid active neutral-point-clamped three-level inverter," in *CPSS Transactions on Power Electronics and Applications*, vol. 10, no. 1, pp. 44–54, Mar. 2025.

- [3] G. Wang, X. Yuan, Y. Jiang, J. Wang, F. Wang, and Z. Liu, "An improved finite control set model predictive control based on a novel dual-port three-level inverter," in *CPSS Transactions on Power Electronics and Applications*, vol. 9, no. 4, pp. 430–442, Dec. 2024.

- [4] C. Qin, X. Li, C. Hou, and C. Su, "A fast-processing implementation method of virtual space vector modulation for the impedance-source three-level inverter," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 71, no. 7, pp. 3568–3572, Jul. 2024.

- [5] C. Wang, Z. Li, X. Si, and H. Xin, "Control of neutral-point voltage in three-phase four-wire three-level NPC inverter based on the disassembly of zero level," in *CPSS Transactions on Power Electronics and Applications*, vol. 3, no. 3, pp. 213–222, Sept. 2018.

- [6] L. M. Halabi, S. S. Hakami, and K. -B. Lee, "Integrated voltage vector-based SVPWM for reliability and performance enhancement of five-level HANPC inverters," in *IEEE Transactions on Industrial Electronics*, vol. 71, no. 2, pp. 1093–1103, Feb. 2024.

- [7] Z. Cai, Y. Du, J. Su, X. Yang, Y. Shi, and J. Zhang, "Comprehensive optimization of ZVS variable frequency control for SiC/Si HANPC converter," in *IEEE Transactions on Industry Applications*, vol. 60, no. 1, pp. 1160–1171, Jan.–Feb. 2024.

- [8] S. Belkhode, A. Shukla, and S. Doolla, "Enhanced hybrid active-neutral-point-clamped converter with optimized loss distribution-based modulation scheme," in *IEEE Transactions on Power Electronics*, vol. 36, no. 3, pp. 3600–3612, Mar. 2021.

- [9] T. Sornsadaeng, P. Chanhom, D. Amorndechaphon, and S. Sirisukprasert, "A strategy for neutral voltage modulation ensuring fault tolerance in CHB multilevel inverters with reduced CMV and unbalanced DC sources," in *IEEE Access*, vol. 12, pp. 154138–154159, 2024.

- [10] Q. Yan, H. Chen, T. Zhao, X. Yuan, L. Zhang, and R. Zhao, "A carrier-based discontinuous space-vector PWM for common-mode voltage reduction in dual-input three-level T-type inverters with unbalanced neutral-point voltages," in *IEEE Transactions on Power Electronics*, vol. 39, no. 9, pp. 11020–11033, Sept. 2024.

- [11] C. Roncero-Clemente, E. Romero-Cadaval, M. Ruiz-Cortés, and O. Husev, "Carrier level-shifted based control method for the PWM 3L-T-type qZS inverter with capacitor imbalance compensation," in *IEEE Transactions on Industrial Electronics*, vol. 65, no. 10, pp. 8297–8306, 2024.

Oct. 2018.

[12] Y. Zou, L. Zhang, Y. Xing, H. Zhang, W. Mo, Y. Wu, and X. Shea, "Enhanced carrier-based discontinuous PWM for three-level inverters with unbalanced neutral-point voltage," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 12, no. 2, pp. 2176–2187, Apr. 2024.

[13] S. Bhowmick, D. Mukherjee, T. S. Basu, and C. Chakraborty, "A three-phase four-leg neutral-point-clamped photovoltaic inverter with decoupled active and reactive power control and DC-link voltage ripple minimization under unbalanced grid operation," in *IEEE Transactions on Power Electronics*, vol. 40, no. 6, pp. 7829–7843, Jun. 2025.

[14] J. Monteiro, V. Fernão Pires, A. Cordeiro, J. F. Silva, and S. Pinto, "Dual three-phase four-leg multilevel inverter with backstepping prediction for unbalanced low-voltage grids," in *IEEE Transactions on Industry Applications*, vol. 61, no. 4, pp. 6535–6546, Jul. -Aug. 2025.

[15] W. Li, X. Zhang, Z. Zhao, G. Zhang, G. Wang, and D. Xu, "Implementation of five-level DPWM on parallel three-level inverters to reduce common-mode voltage and AC current ripples," in *IEEE Transactions on Industry Applications*, vol. 56, no. 4, pp. 4017–4027, Jul. -Aug. 2020.

[16] X. Li, C. Qin, Z. Chu, and J. Fang, "A novel modulation scheme for simultaneous common-mode voltage reduction and neutral-point voltage balance in the reduced switch count quasi-Z-source three-level inverter," in *IEEE Transactions on Power Electronics*, vol. 38, no. 10, pp. 12035–12047, Oct. 2023.

[17] R. H. Cuzmar, A. Mora, J. Pereda, and R. P. Aguilera, "An improved reference generator based on MPC of circulating currents and common-mode voltage for modular multilevel matrix converters," in *IEEE Transactions on Industrial Electronics*, vol. 72, no. 2, pp. 1958–1968, Feb. 2025.

[18] J. Chen, D. Jiang, and Q. Li, "Attenuation of conducted EMI for three-level inverters through PWM," in *CPSS Transactions on Power Electronics and Applications*, vol. 3, no. 2, pp. 134–145, Jun. 2018.

[19] P. Tian, F. Chen, T. M. Jahns, and B. Sarlioglu, "The effect of gate drive resistance on the CM EMI performance of the balanced inverter with asymmetrical parasitic impedance distribution," in *IEEE Transactions on Industry Applications*, vol. 60, no. 6, pp. 9052–9065, Nov.-Dec. 2024.

[20] X. Xing, X. Li, F. Gao, C. Qin, and C. Zhang, "Improved space vector modulation technique for neutral-point voltage oscillation and common-mode voltage reduction in three-level inverter," in *IEEE Transactions on Power Electronics*, vol. 34, no. 9, pp. 8697–8714, Sept. 2019.

[21] X. Xing and H. Chen, "A fast-processing predictive control strategy for common-mode voltage reduction in parallel three-level inverters," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 1, pp. 316–326, Feb. 2021.

[22] P. Liu, S. Duan, C. Yao, and C. Chen, "A double modulation wave CBPWM strategy providing neutral-point voltage oscillation elimination and CMV reduction for three-level NPC inverters," in *IEEE Transactions on Industrial Electronics*, vol. 65, no. 1, pp. 16–26, Jan. 2018.

[23] Z. Wang, J. Teng, M. Zhang, Z. Bu, X. Lin, L. Qi, W. Zhao, X. Li, and X. Sun, "Common-mode voltage suppression strategy for CHB-based motor drive based on topology and modulation optimization," in *IEEE Transactions on Power Electronics*, vol. 40, no. 1, pp. 1697–1716, Jan. 2025.

[24] Z. Chu, C. Qin, X. Li, J. Fang, L. Yang, and Y. Zhang, "Space vector modulation strategy for common-mode voltage suppression in the reduced switch count three-level inverter with unbalanced neutral-point voltages," in *CPSS Transactions on Power Electronics and Applications*, vol. 10, no. 2, pp. 130–140, Jun. 2025.

[25] Y. Zou, L. Zhang, Y. Xing, H. Zhuge, X. Shen, Y. Zhang, and Y. Lu, "An optimized DPWM with reduced leakage current for three-phase three-level inverters with unbalanced neutral-point voltage," in *IEEE Transactions on Power Electronics*, vol. 39, no. 12, pp. 16346–16360, Dec. 2024.

[26] Y. Jiang, X. Li, C. Qin, X. Xing, and B. Zhang, "A generalized modulation method for common-mode voltage reduction of dual-input three-level inverter," in *IEEE Access*, vol. 8, pp. 118762–118772, 2020.

[27] X. Wu, G. Tan, G. Yao, C. Sun, and G. Liu, "A hybrid PWM strategy for three-level inverter with unbalanced DC links," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 6, no. 1, pp. 1–15, Mar. 2018.

[28] C. Qin, X. Li, X. Xing, C. Zhang, and G. Zhang, "Common-mode voltage reduction method for three-level inverter with unbalanced neutral-point voltage conditions," in *IEEE Transactions on Industrial Informatics*, vol. 17, no. 10, pp. 6603–6613, Oct. 2021.

**Chuanjing Hou** received the Ph.D. degree in Control Science and Engineering from Shanghai Jiao Tong University, Shanghai, China, in 2018. He is currently an Associate Professor with the School of Information and Electrical Engineering, Shandong Jianzhu University. His research interests include high-gain multilevel inverter.

**Desheng Jia** received the B.S. degree in Electrical Engineering and Automation from Weifang University of Science and Technology University, Weifang, China, in 2022. He is currently pursuing the M.S. degree in Control Engineering with Shandong Jianzhu University, Jinan, China. His current research interests include SiC&Si hybrid ANPC three-level inverter.

**Changwei Qin** received the Ph.D. degree in Electrical Engineering from Shandong University, Jinan, China, in 2019. In 2020, he joined Shandong Jianzhu University, where he is currently an Associate Professor. His current research interests include control of multi-level converters and impedance source converters.

**Xiaoyan Li** received the Ph.D. degree in Electrical Engineering from Shandong University, Jinan, China, in 2020. From 2021 to 2023, she was a Postdoctoral Research Fellow with Shandong University, Jinan, China. In 2023, she joined Shandong Jianzhu University, where she is currently a Professor. Her current research interests include control of multi-level converters and power quality control.

**Jiandong Li** received the B.S. degree in Building Electrical and Intelligence from Shandong Jianzhu University, Jinan, China, in 2023. He is currently pursuing the M.S. degree in control engineering with Shandong Jianzhu University, Jinan, China. His research interests focus on multilevel inverters.